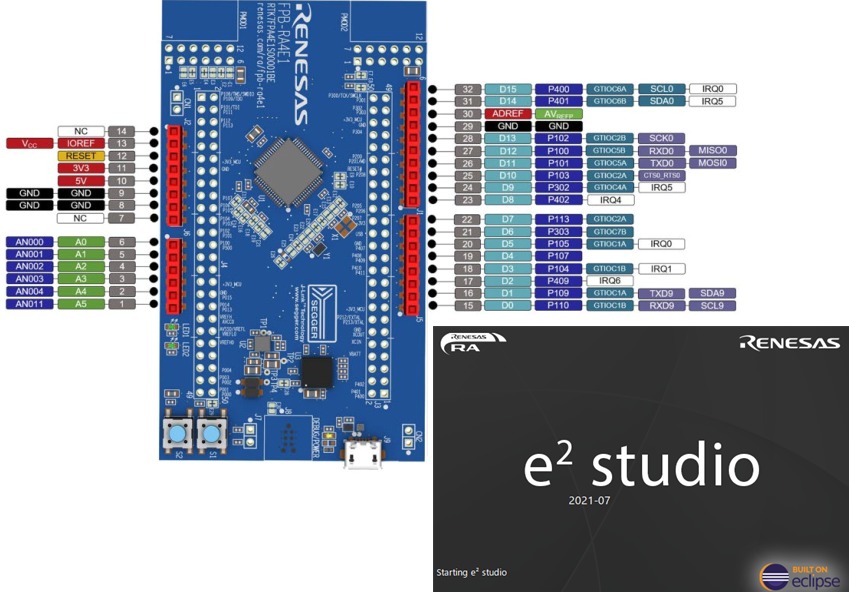

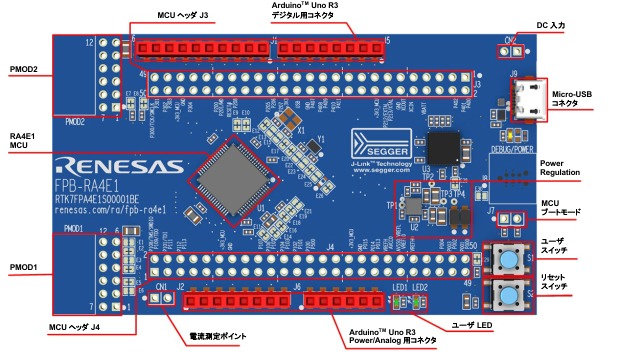

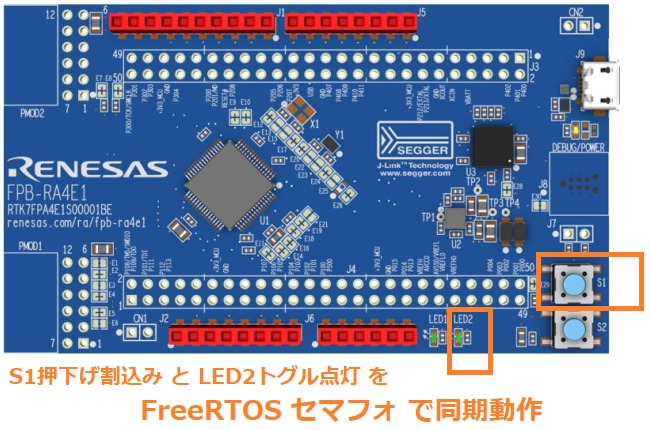

RAファミリ評価ボードRA4E1 Fast Prototype Board (Cortex-M33/100MHz、Flash/512KB、RAM/128KB)(以降FPB)の、スイッチS1でLED2を点灯するFreeRTOS適用例を示します。RAファミリビギナーズガイド9章記載のEK-RA6M4評価キットを使った処理内容と同じです。

e2 studio 2021-10は、Project>Change Deviceで対象MCUデバイス変更機能がありますが動作しません。そこで、ガイド掲載のEK-RA6M4を手動でRA4E1へ変更し、FPBでFreeRTOSのセマフォを利用し、S1押下げ割込みとLED2トグル点灯を同期させるFreeRTOSサンプルコードを示します。

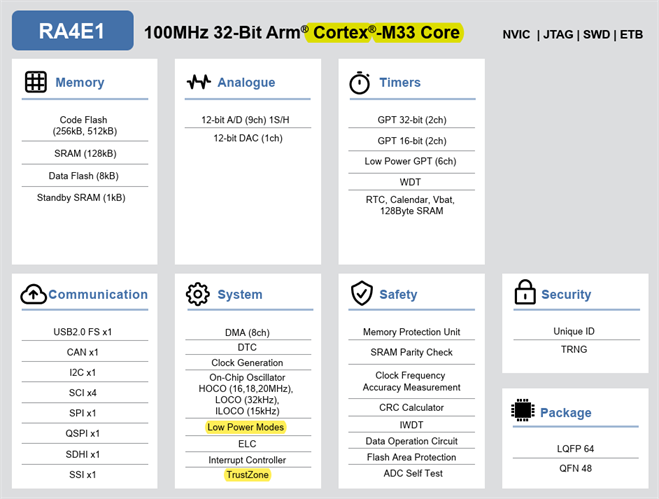

このコードを使い、前稿よりも具体的にFPBとFlexible Software Package(以降FSP)の使い方、今回は使わないTrustZoneのメリットを示すのが、本稿の目的です。

RA4E1 Fast Prototype Board(FPB)のRTOSとTrustZone

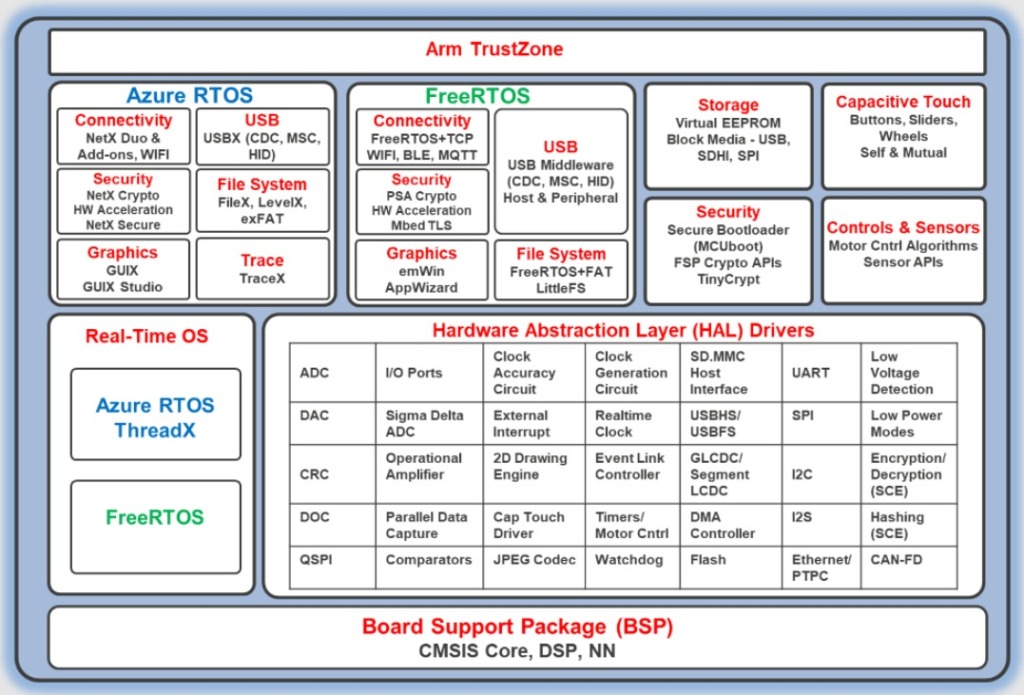

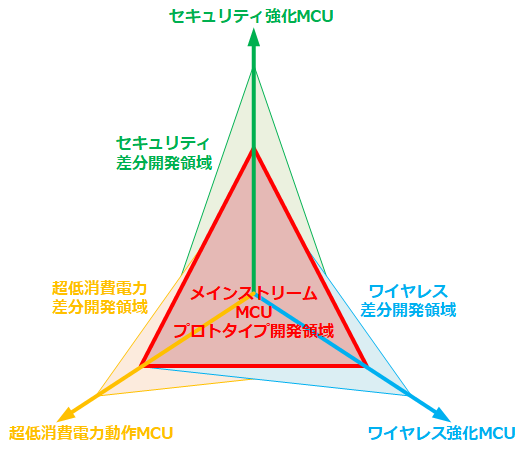

IoT MCUをクラウド接続するには、RTOSが必要です。AWS(Amazon Web Services )接続にはFreeRTOSライブラリ、Microsoft Azure接続にはAzure RTOSライブラリの利用が前提だからです。

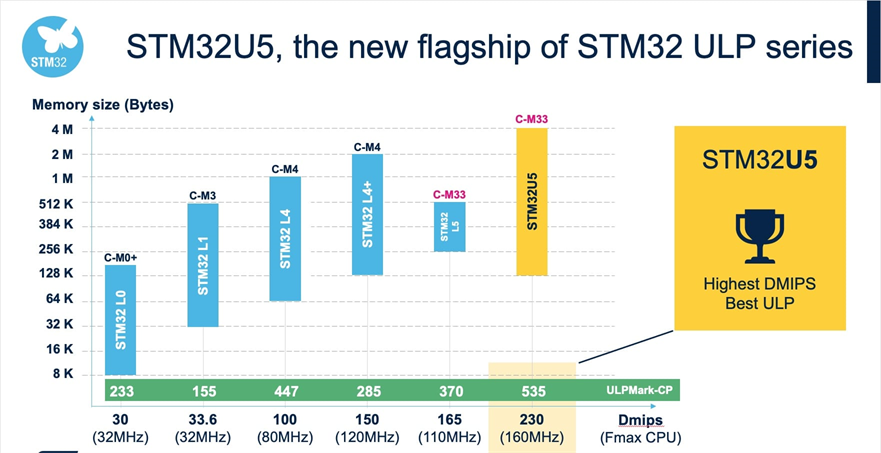

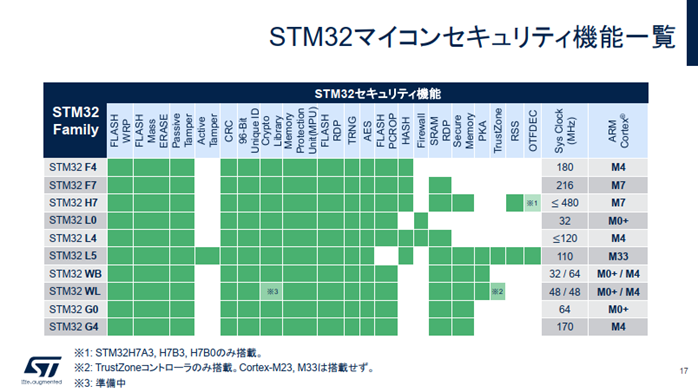

また、クラウド接続には、TrustZoneなどハードウェアによるセキュリティ対策も要求されますので、RTOSとTrustZoneは、IoT MCUの必須2技術です。

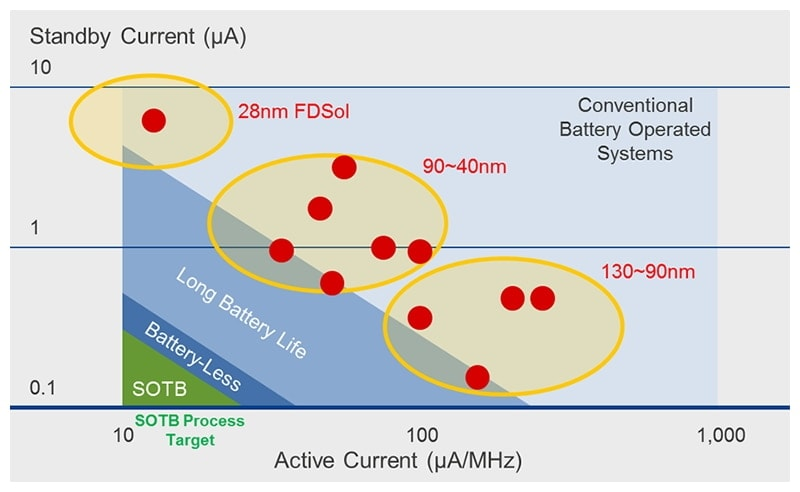

ハードウエアセキュリティは、開発後、簡単に追加することが困難です。今回はTrustZone未使用ですが、IoTプロトタイプ開発にTrustZone内蔵Cortex-M33を用いるのは、例え未使用でも製品セキュリティ処理の具体的検討ができるなど、IoTセキュリティを開発初期から考慮した設計となるからです。

これが使わないTrustZoneのメリットです(TrustZone使用例も、いずれ投稿予定)。

本稿は、先ずFreeRTOSをFPBへ適用します。FreeRTOS新規プロジェクト作成、API生成ツールFSP設定、FSP生成ファイルへのタスク追記の順に説明します。

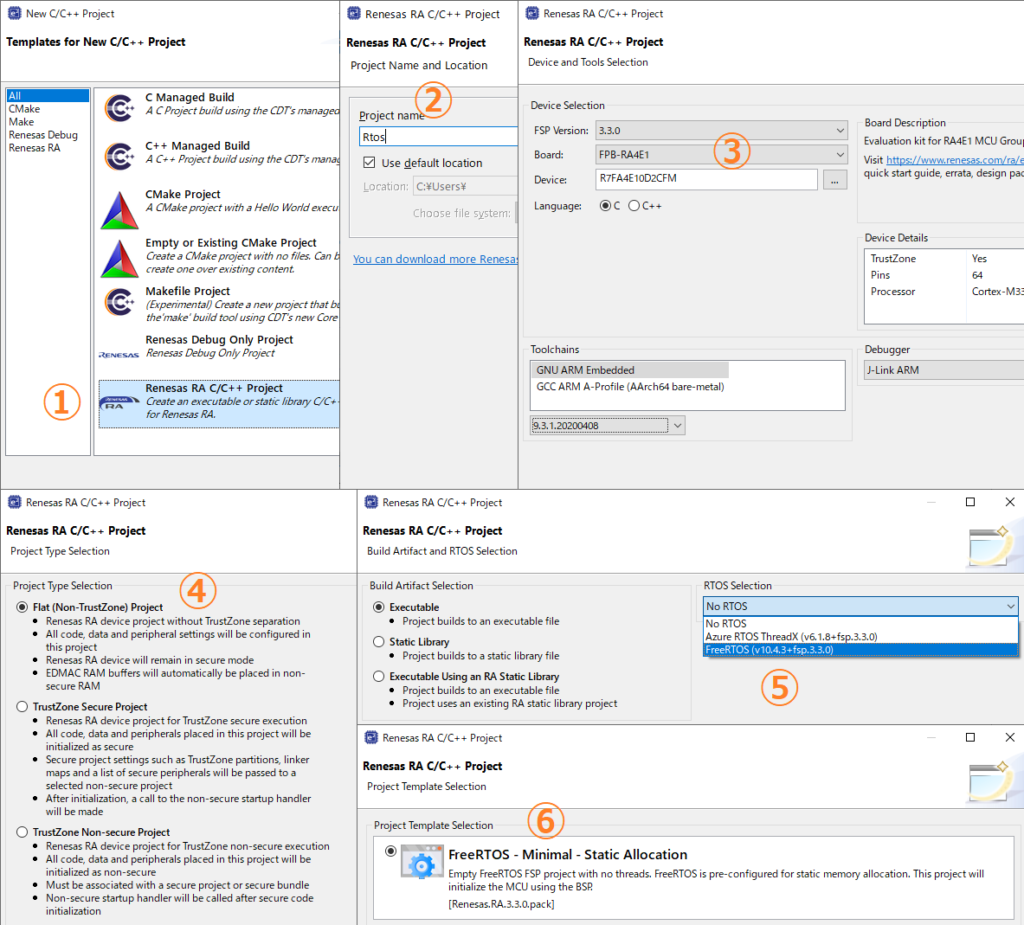

Step1:FreeRTOS新規プロジェクト作成

最新版e2 studio(2021-10)の新規FreeRTOSプロジェクトは、File>New>C/C++Projectとクリックし、①~⑥の手順で作成します。

②プロジェクト名は、任意です。③Boardは、PFB-RA4E1を選択します。

④TrustZone未使用時のプロジェクトを、“Flat”と呼びます。これは、TrustZone使用時、セキュアと非セキュアの2プロジェクト並存が必要となりメモリ領域を分割することに対する、平坦なメモリ使い方に起因していると思います。

※メモリ領域分割は、PCハードディスクのパーティション分割をイメージして頂ければ判り易いでしょう。例えサイバー攻撃を受けても、物理的に侵入できないメモリ領域を作り、ここへ最重要情報やソフトウェアを保存する訳です。

⑤FreeRTOSを選択します。ベアメタル(No RTOS)とAzure RTOSも選択可能です。⑥Minimalを選択し、FinishクリックでFreeRTOS(TrustZone未使用)新規プロジェクトが完成です。

各選択肢を変えると、前稿で説明した多種類の新規プロジェクトが作成できることが解ります。

Step2:Flexible Software Package(FSP)設定

新規プロジェクト作成のFinishクリックで、FSPパースペクティブオープンを聞いてきますので、開きます。

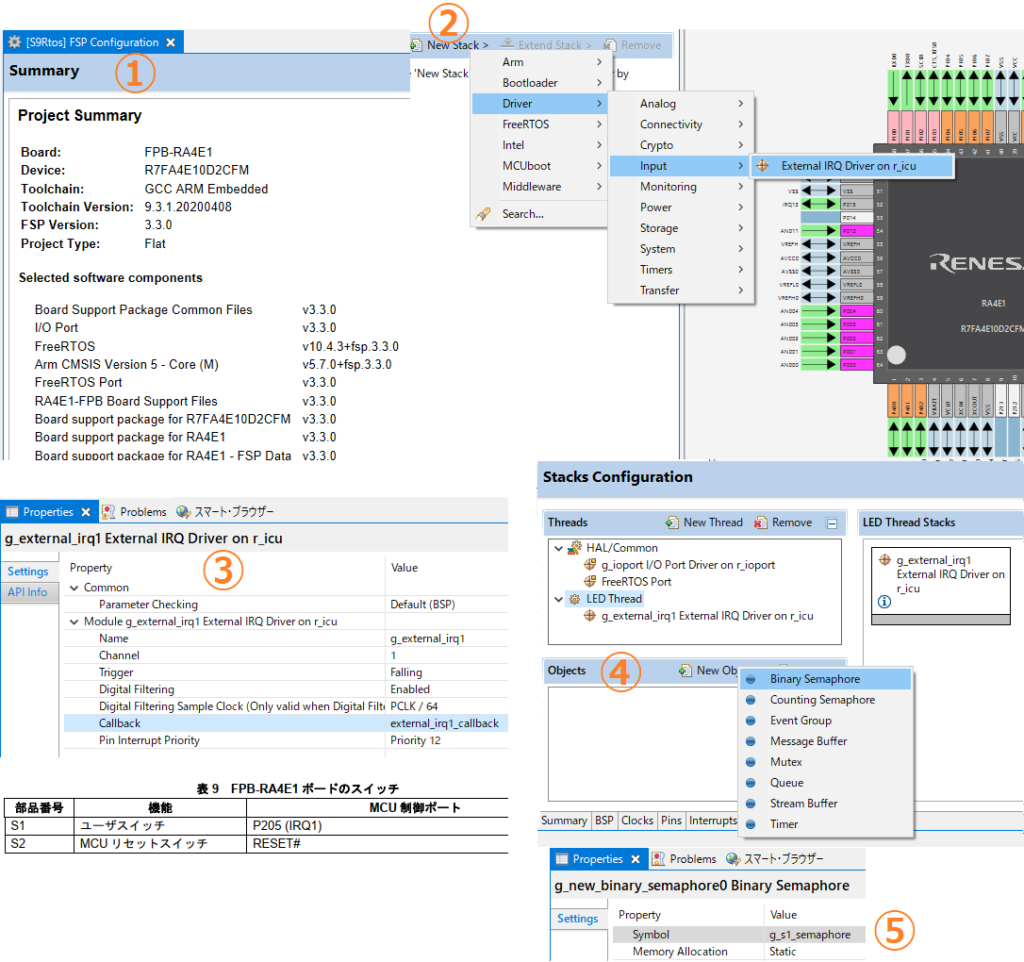

①プロジェクトSummaryが表示されます。Stacksタブを選択、②New Stackをクリックし、External IRQ Driver on r_icuを選択します。新しい外部割込みドライバがStackに追加され、③プロパティが表示されます。

FPBのユーザスイッチS1は、P205(IRQ1)に接続済みです。そこで、③プロパティのirq0をirq1、TriggerをFalling、Digital FilteringをEnable、Callbackをexternal_irq1_callbackに変更します。

次にセマフォ追加のため、④ObjectsのNew Objectsをクリックし、Binary Semaphoreを選択します。⑤プロパティSymbolをg_s1_semaphoreに変更します。

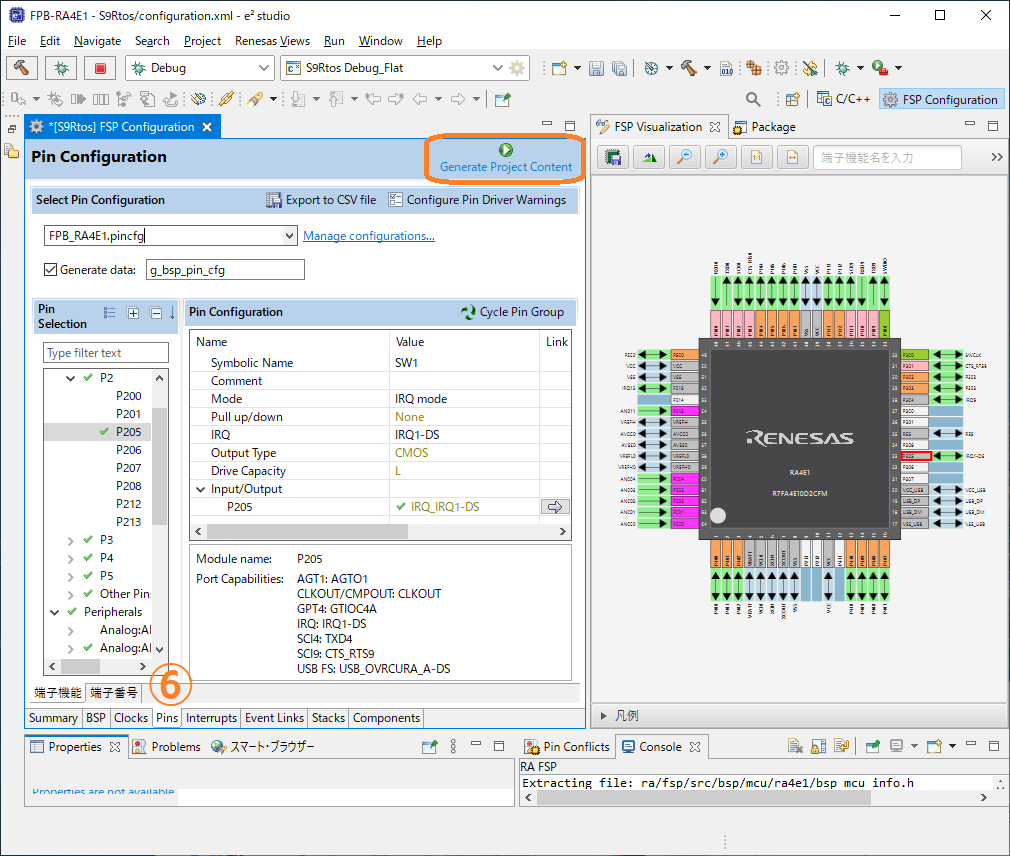

最後に、⑥pinsタブをクリックし、ユーザスイッチS1:P205(IRQ1)とIOピン割当てをGUIで確認します。

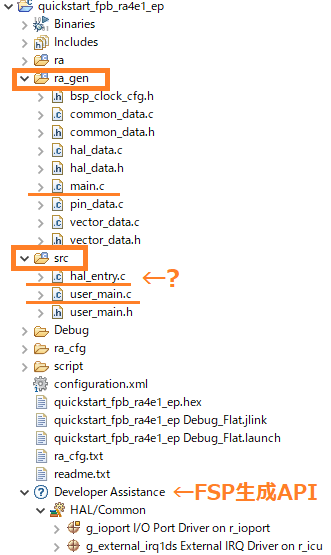

以上でFSP設定は完了です。Generate Project Contentをクリックすると、APIや割込みコールバック関数、関連ファイルが自動生成されます。

Step3:FSP生成ファイルへタスク追記

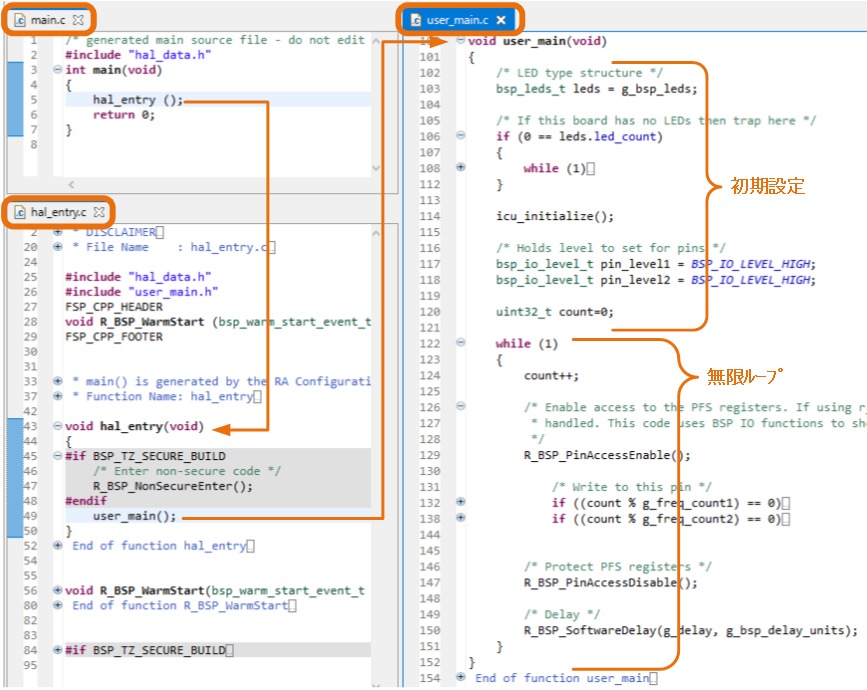

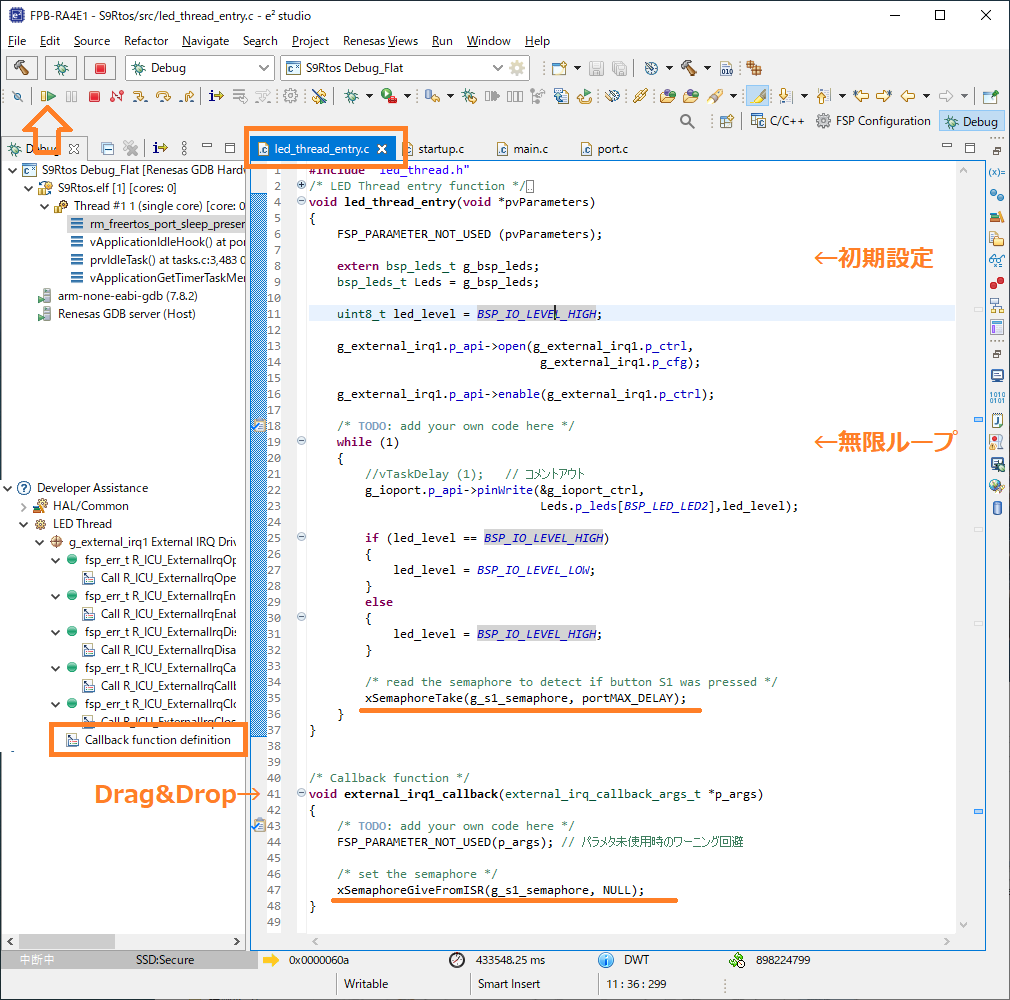

FSPが生成したファイル:led_thread_entry.cに上記コードを追加します。このコードは、LED初期化と無限ループ処理から構成されます。RAビギナーズガイド掲載のirq10をirq1へ変更したLEDタスクです。

コールバック関数external_irq1_callbackは、Developer AssistanceのLED Threadを開くと一番下に割込みコールバック関数が生成済みですので、これをドラッグ&ドロップして追加します。

LEDタスク追加後、ビルドしFSBへダウンロード、デバッガ起動後、再開を2回クリックして実行中の様子が上図です。FSBのS1クリックでLED2がトグル点灯します。

FreeRTOS Queueサンプルコード

前章は、RAファミリビギナーズガイド9章のEK-RA6M4評価キットFreeRTOSセマフォサンプルコードを、RA4E1 Fast Prototype Board(FPB)へ流用したコードです。変更箇所は、irq10をirq1へ変えただけです。

FSPには、FreeRTOS Queueサンプルコード:freertos_fpb_ra4e1_epも付属しています。これら2つのサンプルコードを理解すれば、セマフォとQueueを使う基本的なFreeRTOSソフトウェア開発が可能です。

FreeRTOS待合せ手段としては、セマフォ/Queue以外にもMutexやイベントグループなどの手段もあります。弊社ではFreeRTOS基礎固めを目的として、Hardware Independent FreeRTOS Exampleを応用したセマフォ/Queue活用のFreeRTOSテンプレート化を目指しています。RA/REテンプレートもこの方針で開発する予定です。

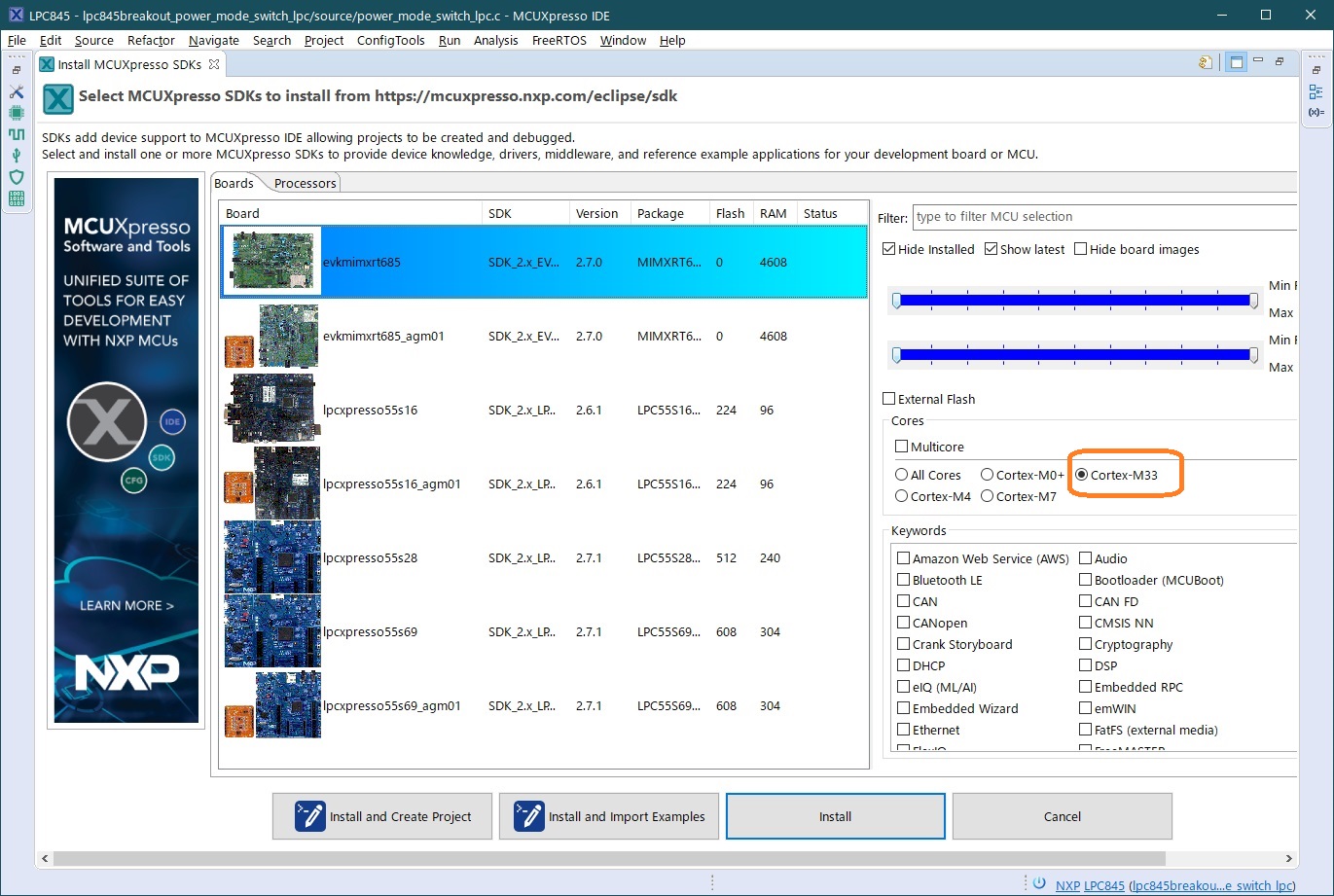

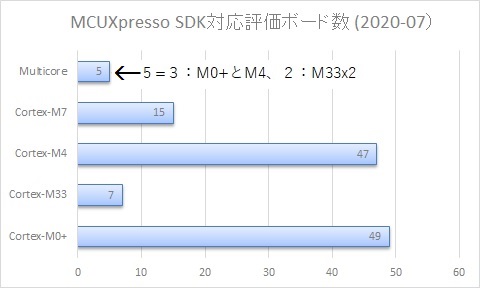

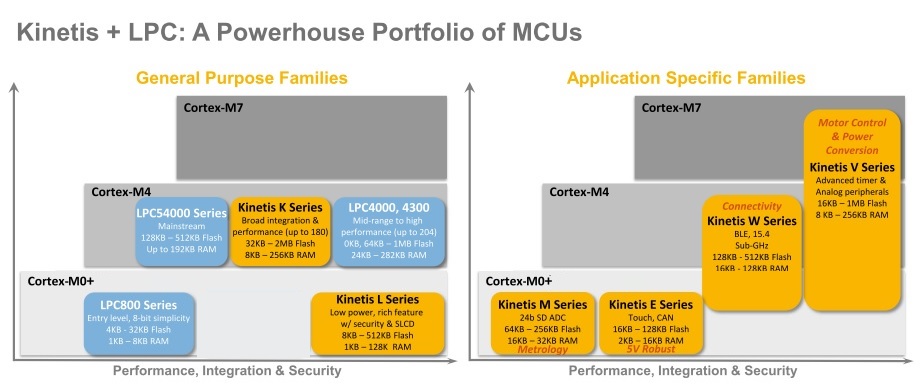

この方針で開発したNXP版FreeRTOSアプリケーションテンプレートは、コチラから概要がダウンロード可能です。

まとめ

RA4E1 Fast Prototype Board(FPB)へ、RAファミリビギナーズガイド掲載FreeRTOSサンプルコードを流用し、ユーザスイッチS1とLED2点灯をセマフォで同期させました。

FreeRTOS新規プロジェクト作成、Flexible Software Package(FSP)設定、FSP生成ファイルへのタスク追記の具体的操作手順を示しました。

ガイド9章には、更に詳細な説明がありますので、参考になります。例えば、スイッチ割込み優先度12を利用する理由、systick優先度15が予約済みであるなどです。

TrustZoneは未使用ですが、プロトタイプ開発初期からIoTセキュリティを考慮した設計ができるメリットがあります。

FSP付属Queueサンプルコードと本セマフォコードを使ってFreeRTOS基礎固め目的のRA/REテンプレート開発を進めます。