Cypress PSoC 4 MCU内蔵タッチセンサ:第4世代CapSenseの使い方、最終回は、これまでの関連投稿全体まとめと、PSoC MCU開発時の留意点を説明します。

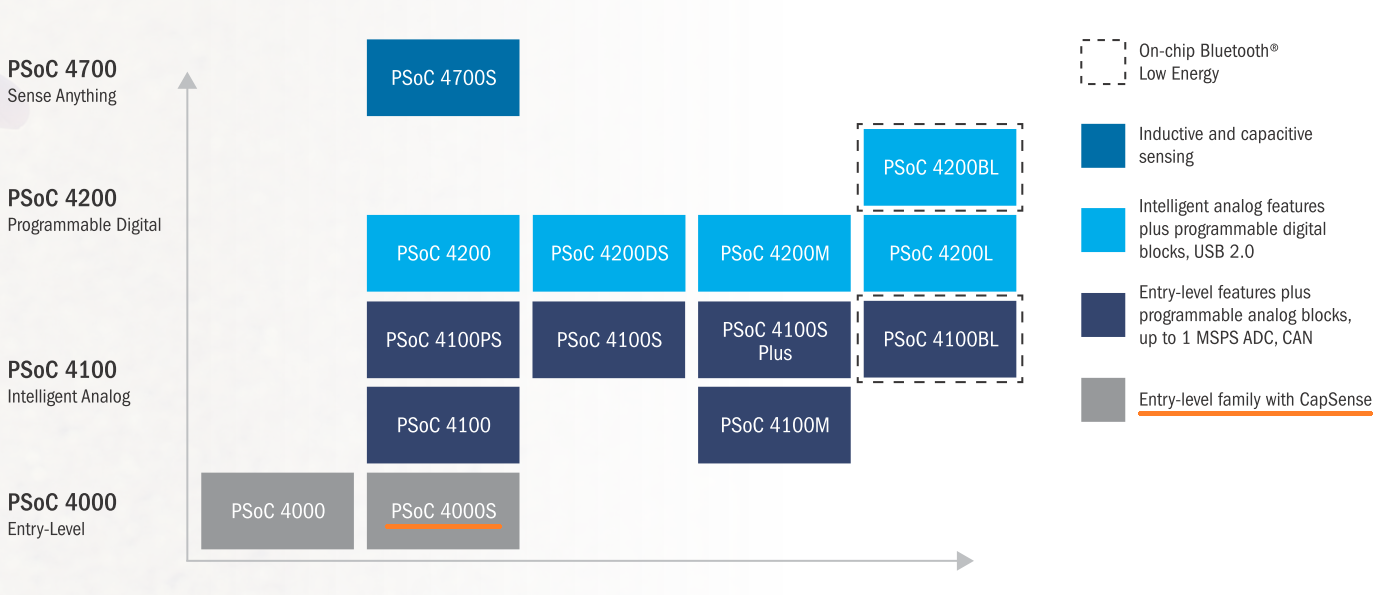

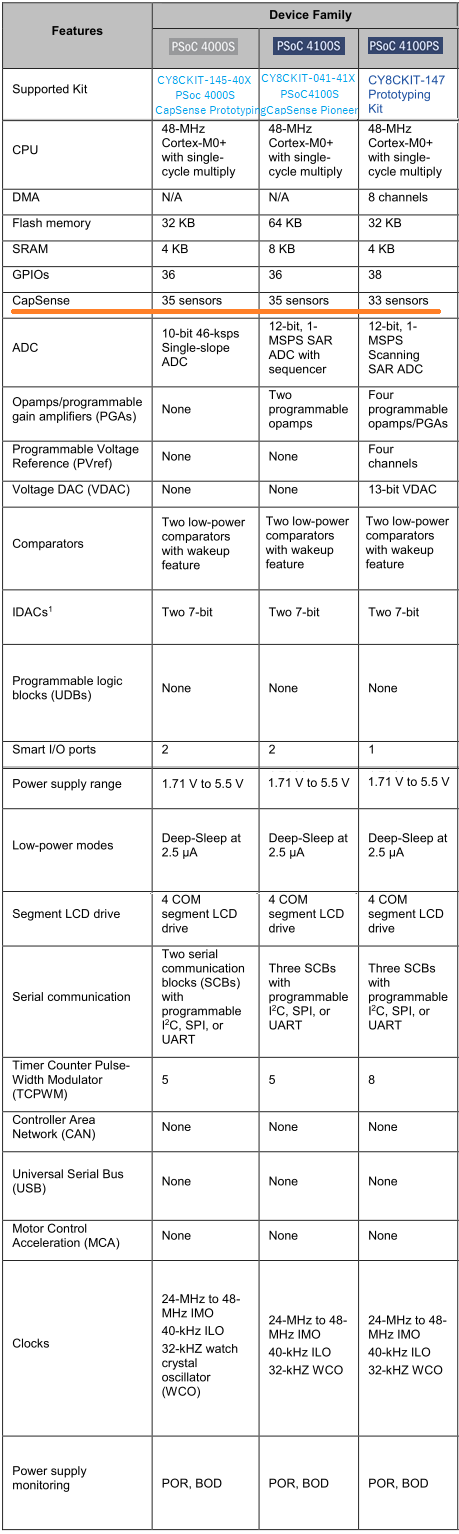

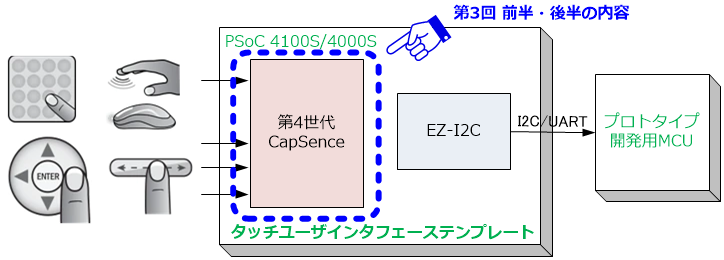

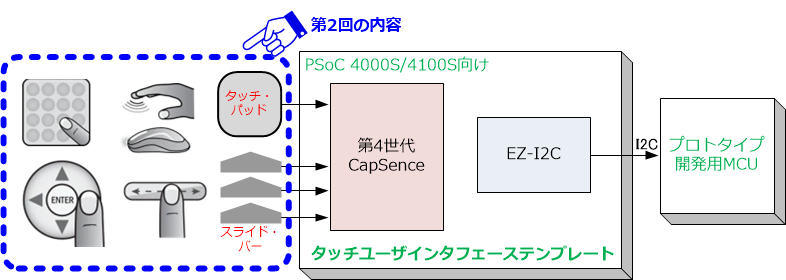

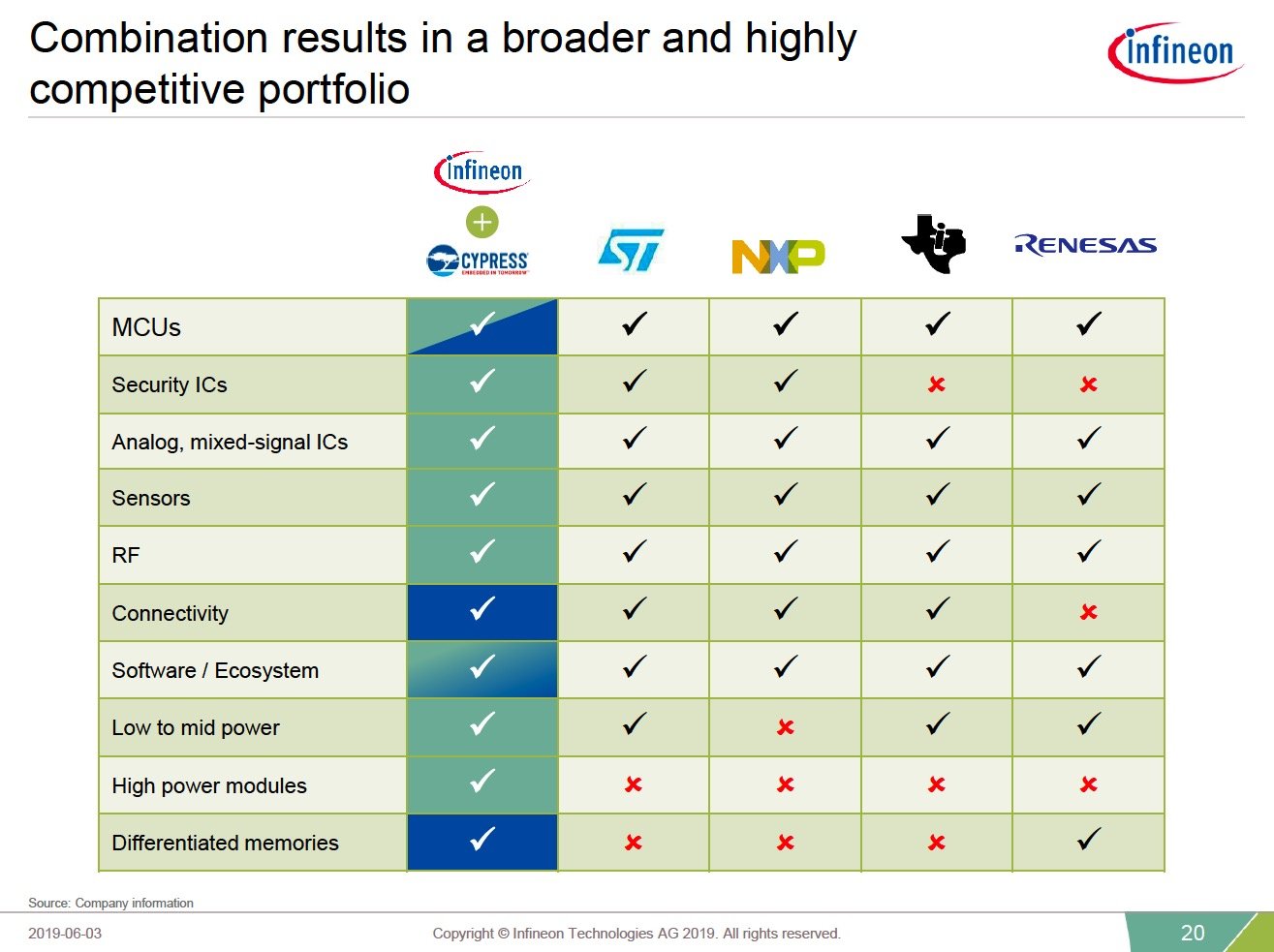

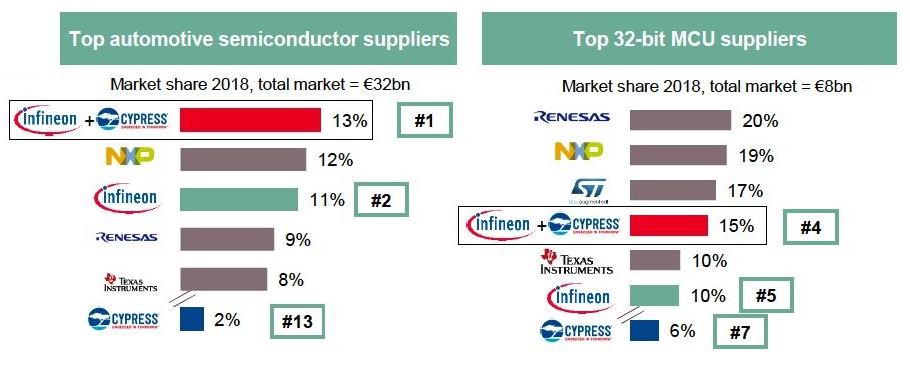

6月3日発表のInfineon+Cypressが成立するかは不透明です(関連投稿:InfineonがCypress買収で合意 )。但し、買収が成立するとCypressのPSoC 4シリーズはよりメジャーMCUになります。このPSoC 4000S/4100S内蔵の最新第4世代CapSense使ったタッチUIテンプレート開発が関連投稿の目的です。

PSoC MCUのソフトウェア開発は、他社ARMコアMCU開発と比べると少々クセがあります。

但し、このクセさえ知っていれば、他社MCUからの移行も容易で、PSoCの特徴を活かした開発もできます。そこで、このクセに対する個人的な留意点と、開発に使用した評価ボードのTipsを初めに示します。

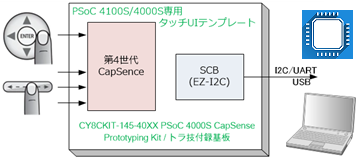

第1回~今回の投稿を基に、PSoC 4000S/4100S専用タッチUIテンプレート開発を進めます。開発完了とテンプレート発売は、少し時間を頂いて、2019/3Qを予定しております。

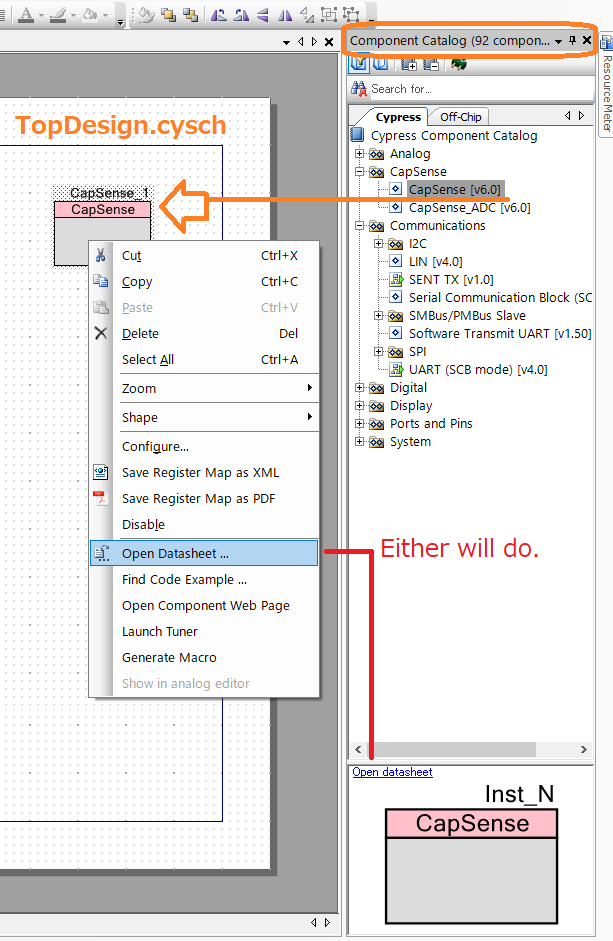

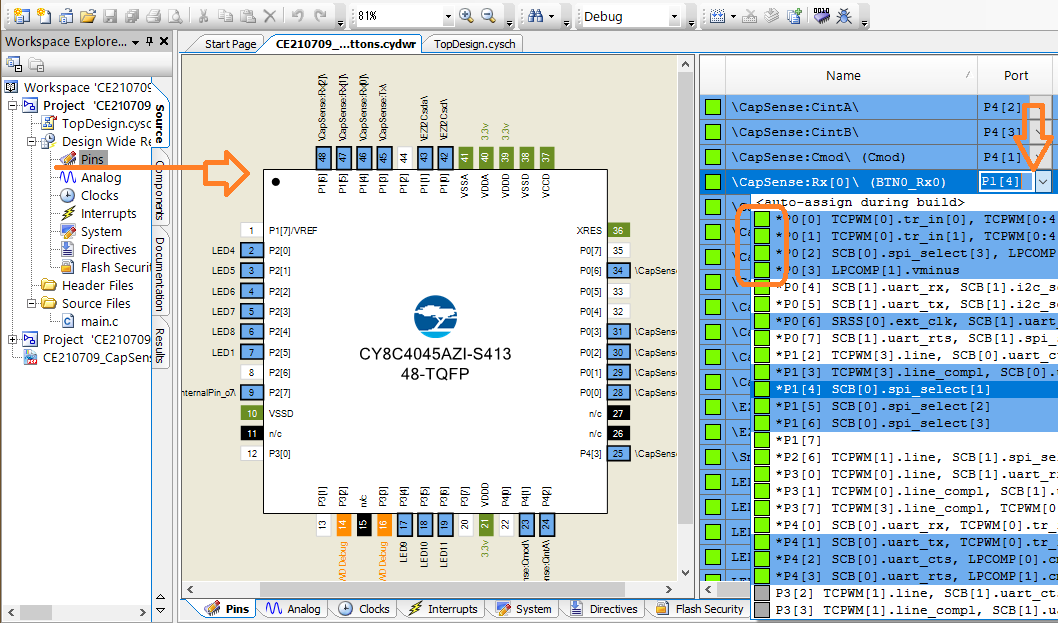

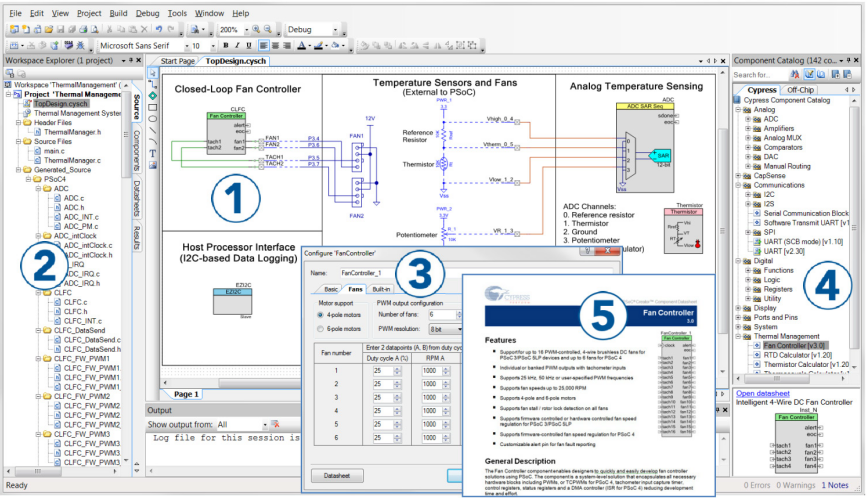

PSoC MCU開発時の留意点、評価ボードTips 用語とPSoC Creator Cypress PSoC MCU資料で用いる用語は、他社が使う一般的な用語と異なります(対応表参照)。また、PSoC CreatorのTopDesign.cyschと呼ぶ回路図へコンポーネントを配置し、開発着手するのも他社に無い手法です。

Cypress PSoC MCU 用語 他社ARM コアMCU 用語

ファームウェア:Firmware

ソフトウェア

コンポーネント:Component

ハードウェア、周辺回路、コントローラ

コードサンプル:Code Example

サンプルプロジェクト、サンプルソフトウェア

PSoC CreatorのTopDesign.cysch(論理回路図)

なし

PSoC Creatorも他社同様EclipseベースIDEです。しかし、PSoC MCUの独特な設計手法(これをクセと表現しました)をサポートする強力かつ良くできたツールです。画面構成が他社Eclipse IDEと異なりますが、注意して画面を観察すると、開発中に知りたいリンクがほぼ100%あります。

Cypressは、PSoC/PRoCをMCU:マイコンというより、むしろ、プログラミングも可能なASIC(PSoCがProgrammable System-on-Chipの略から筆者推測)のように考えているため、これらのクセが生じるのだと思います。

Cypress資料 Cypress資料は、質・量・書き方ともに優れています。英語ですが、日本語版もありますので、是非資料を読むことをお勧めします。内容は整理されており、解り易いので、目次のみ見てもほぼ解ります。

筆者はせいぜい数時間しか集中できません。集中力が持続しない方にお勧めの情報把握方法が、目次のみ → 内容類推 → 内容把握です。コンポーネント習得と同様、焦らず段階的、部分的に把握していけば、そのうち全体が見えてきます。

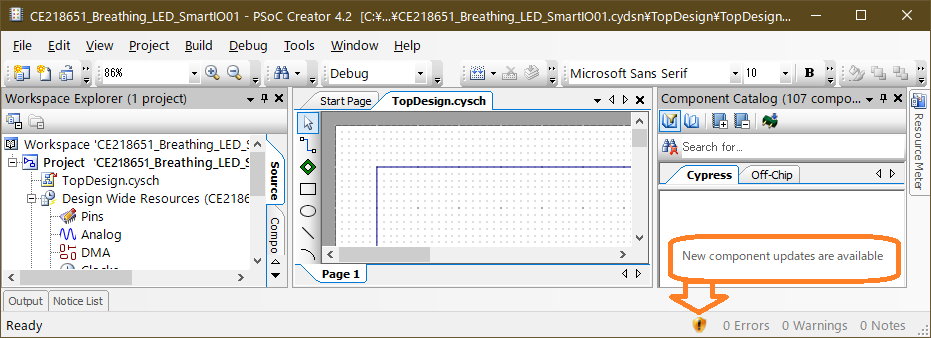

コンポーネントUpdate PSoC MCUのソフトウェア開発は、コンポーネントAPIのプログラミングです。想定するアプリケーション用に各種コンポーネントを組み合わせて入れた容器、これがデバイスです。

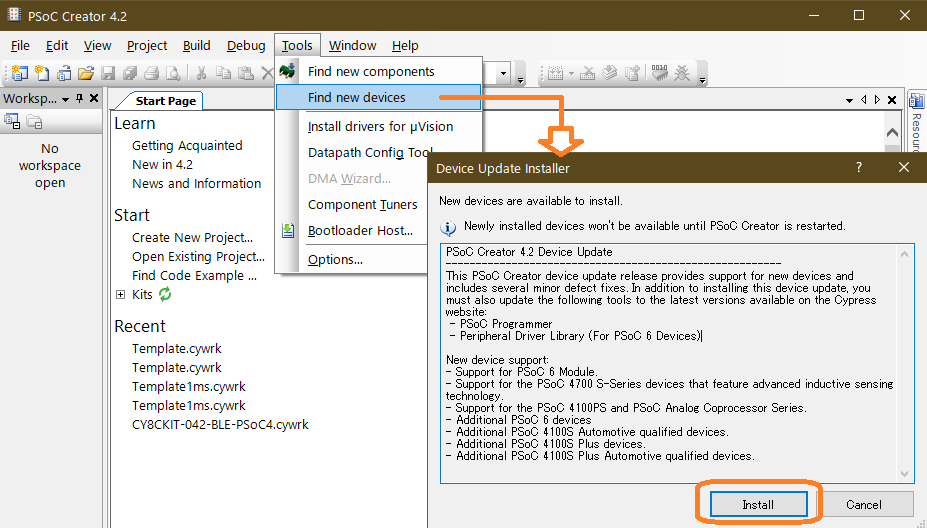

コンポーネントは、それ自身が更新されバージョンを持ちます。例えば、第4世代CapSenseコンポーネントの最新バージョンは、2019年6月現在6.0です。PSoC Creator起動時に、プロジェクト使用中コンポーネント版数を自動的に調べ、Updateがある場合には、Notice Listに通知されます。

殆どの場合、コンポーネントをUpdateしてもトラブルはありません。しかし、コンポーネントUpdateがデバイスハードウェア/ソフトウェア両方に関係するため、コンパイルNGなどになることも稀にあります。

従って、Update時にはArchivesを作成し、元に戻せるようにしましょう。Archives作成は、PSoC CreatorがUpdate時にダイアログを示しますので従ってください。

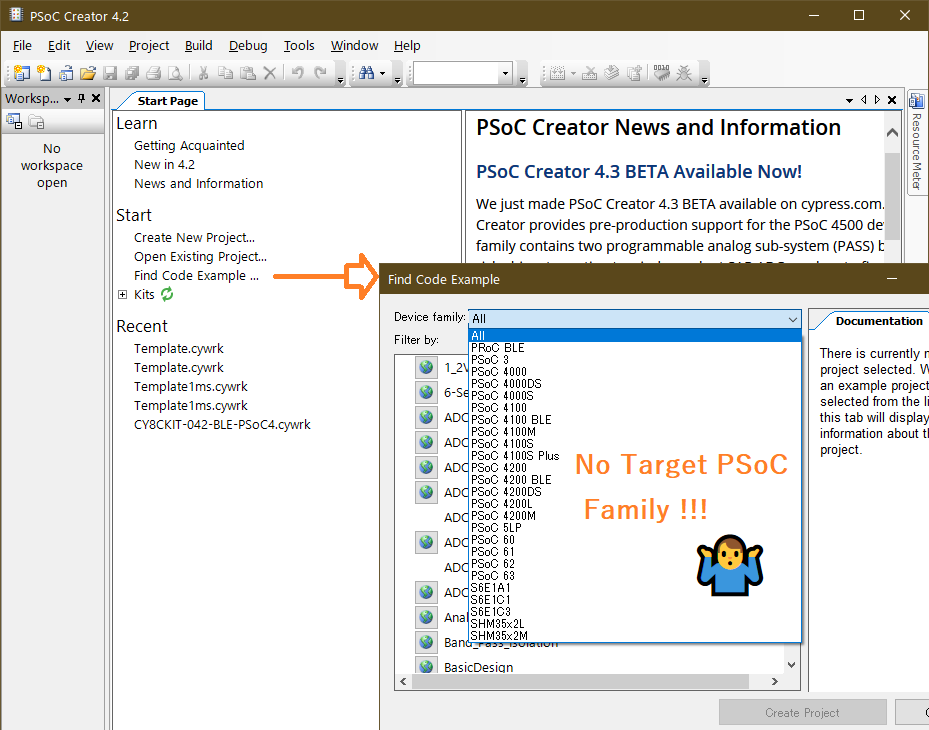

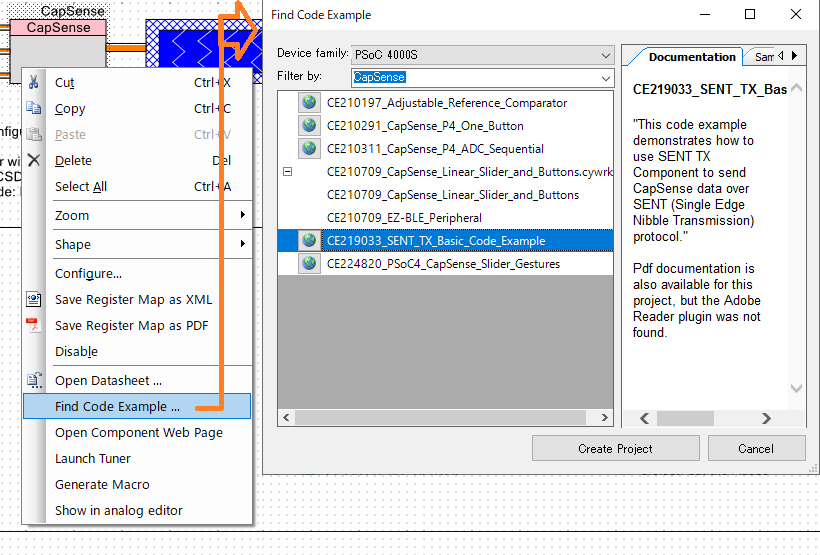

コンポーネントCode Example コンポーネント毎にCode Exampleがあります。PSoC Creatorのコンポーネントカタログ掲載のコンポーネントは、いわば標準的なもので、Code Exampleの中には、巧みな使い方をした派生コンポーネントもあります。

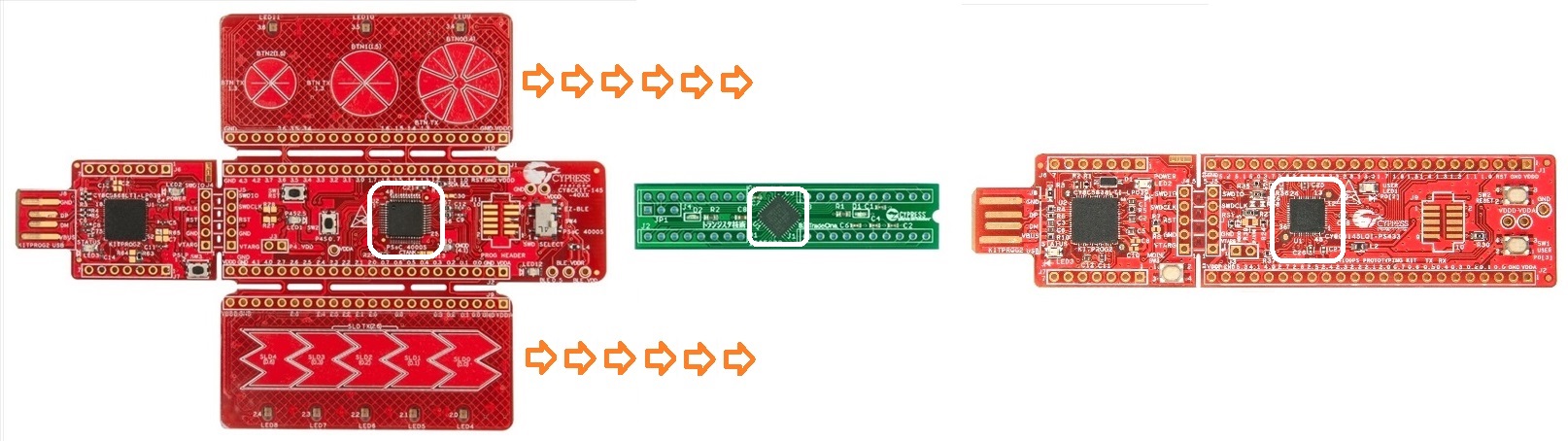

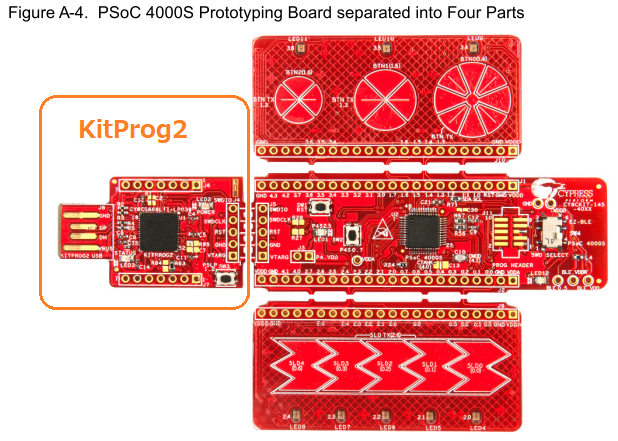

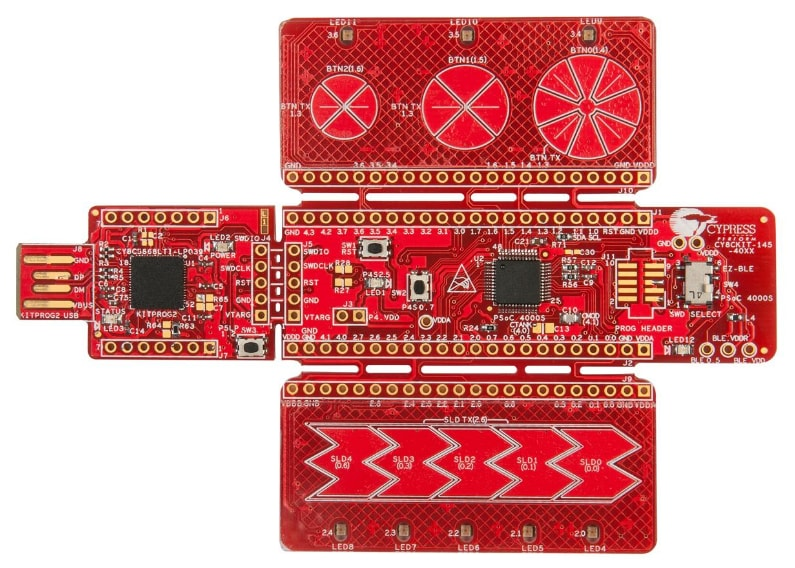

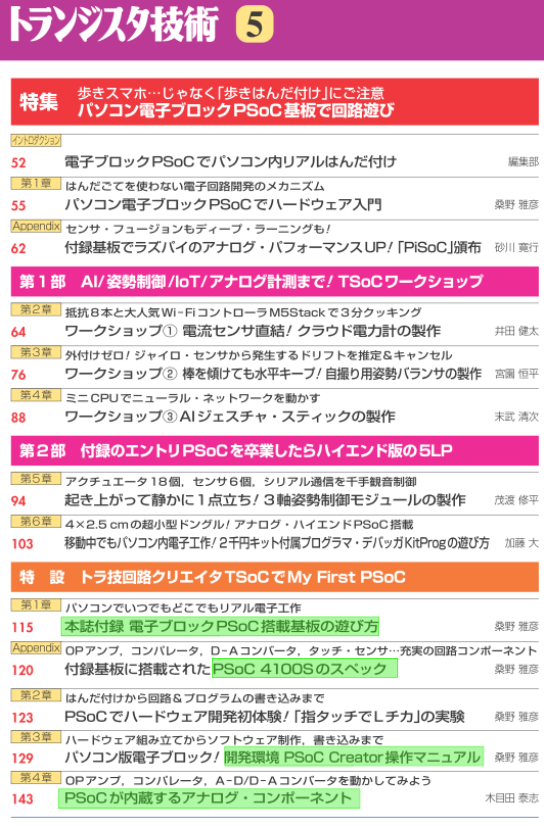

CapSenseのCode Example検索方法 評価ボード:KitProg2 本開発で用いた評価ボード:CY8CKIT-145-40XX PSoC 4000S CapSense Prototyping Kit のKitProg2基板は、2019年5月号トラ技第6章P103~P114のPSoC 5記事のことです。

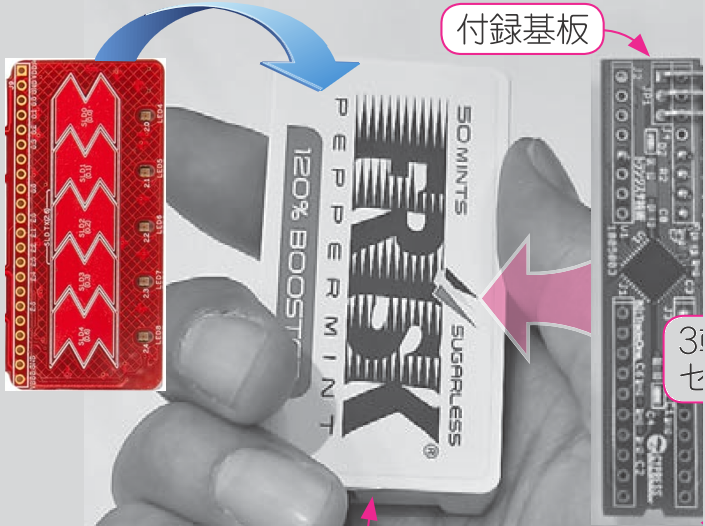

評価ボードのKitProg2部分(出典:PSoC 4000S Prototyping Kit Guide) 筆者はこのPSoC 5搭載KitProg2基板を、トラ技付録基板に接続する予定です。つまり、トラ技記事では別途購入が必要であったUSBシリアル変換アダプタの代わりに、トラ技付録基板へのテンプレートプログラミングやデバッグに活用します。

もちろんKitProg2基板は、トラ技6章記事のような使い方もできます。

KitProg2基板は、「SWD(Serial Wire Debug)を使った“汎用”のPSoC MCUプログラミングインタフェースモジュール」です。

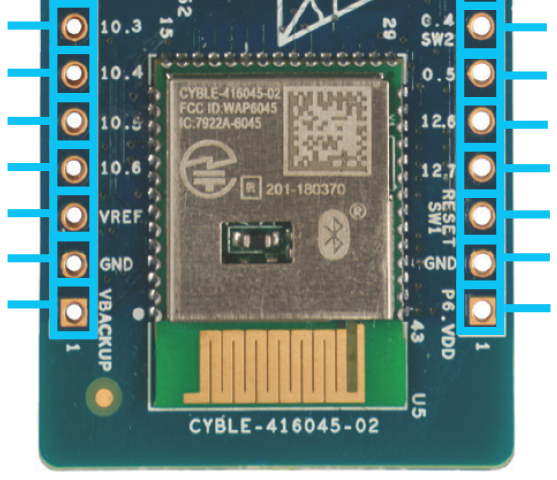

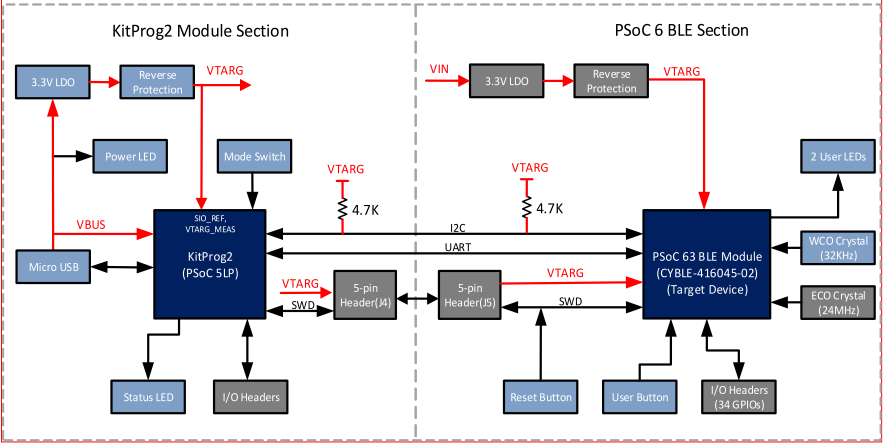

KitProg2とPSoC 6の接続例(出典:CY8CPROTO-063-BLE Schematic) 上図はPSoC 6がターゲットMCUの例です。ターゲットMCUとSWD IO/SWD CLK+RST/GND/VTARGの5ピンで接続すれば、USB接続のKitProg2モジュール経由でPSoC Creatorプログラミング/デバッグが可能です。

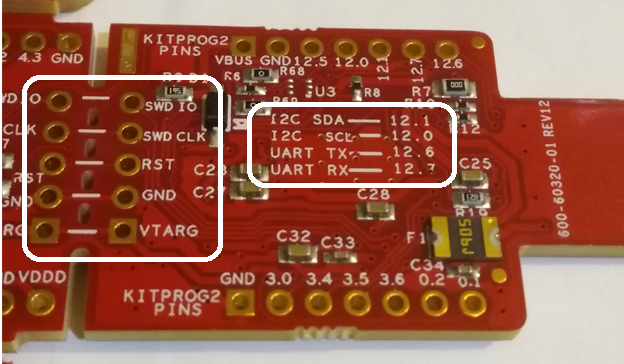

また、USB ⇔ I2C/シリアル変換アダプタとして利用する場合は、KitProg2裏面掲載のターゲットMCUとの結線追加で可能です(評価ボードI2C、UARTは、基板内で配線済み)。

KitProg2裏面のターゲットUARTとI2Cの結線(中央) USB ⇔ I2C変換アダプタ利用時はPSoC Creator付属Bridge Control Panel、また、USB ⇔ UART変換アダプタ利用時はTera Termなどが接続ツールとして使えます。

開発するCapSense UIモジュールと外部機器、または別MCUとの接続デバッグ時に、上記KitProg2基板のUART、または、I2Cの変換アダプタ機能が活用できます。

その4で示したSCBコンポーネントの3モードのうち、UART/I2Cがこれら変換アダプタ経由でPCとの通信に使えます。従って、SCBコンポーネントを手軽に使うには、接続ツールが用意されているUART/I2Cが適しています。

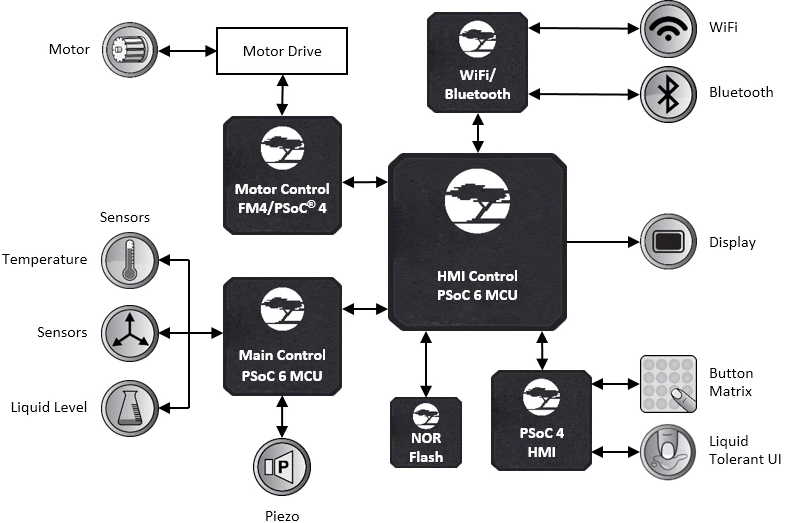

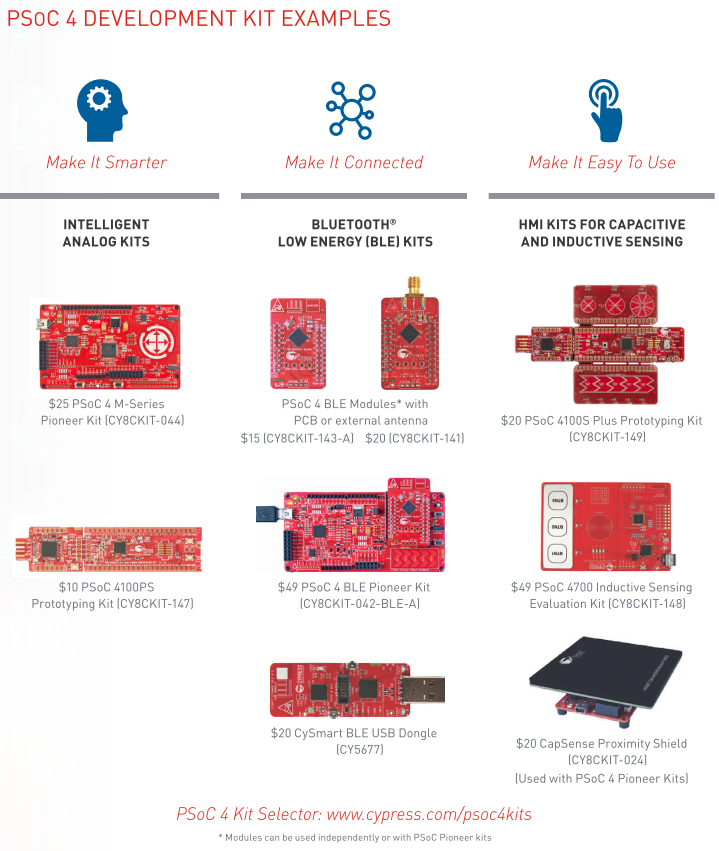

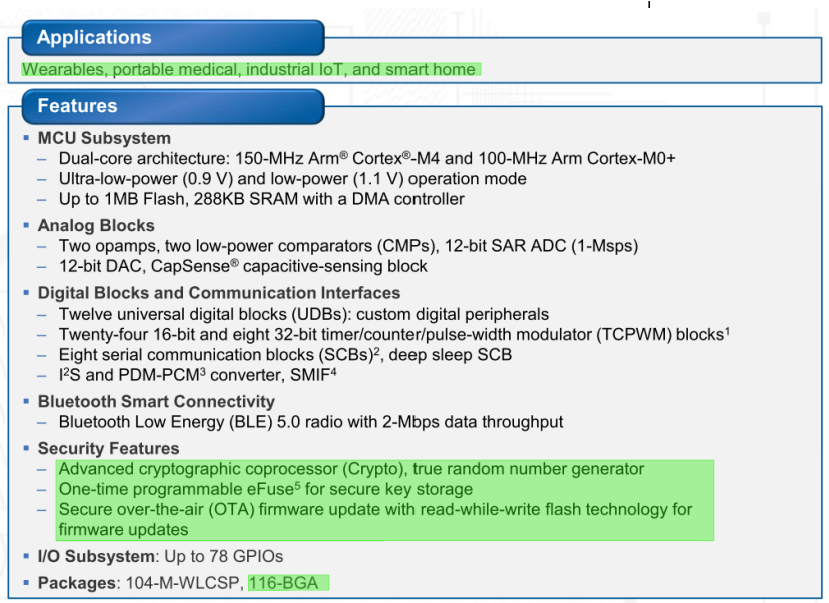

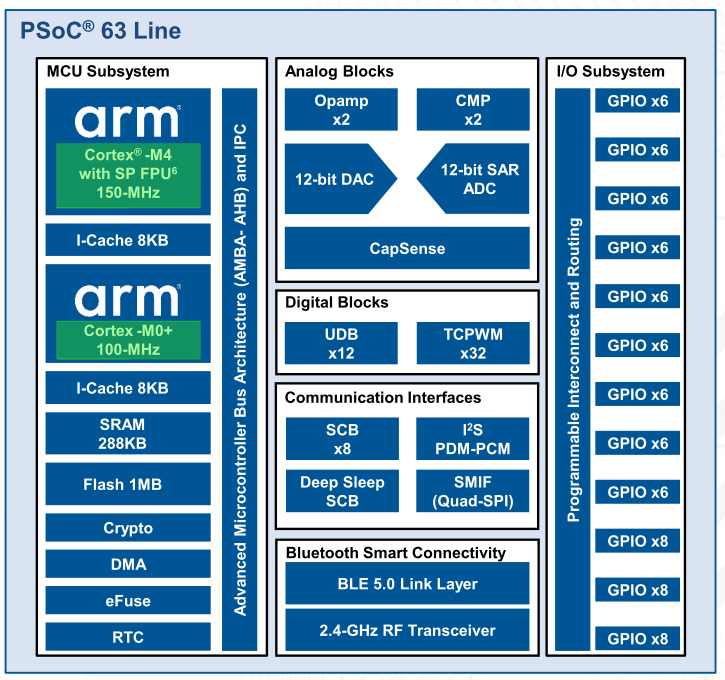

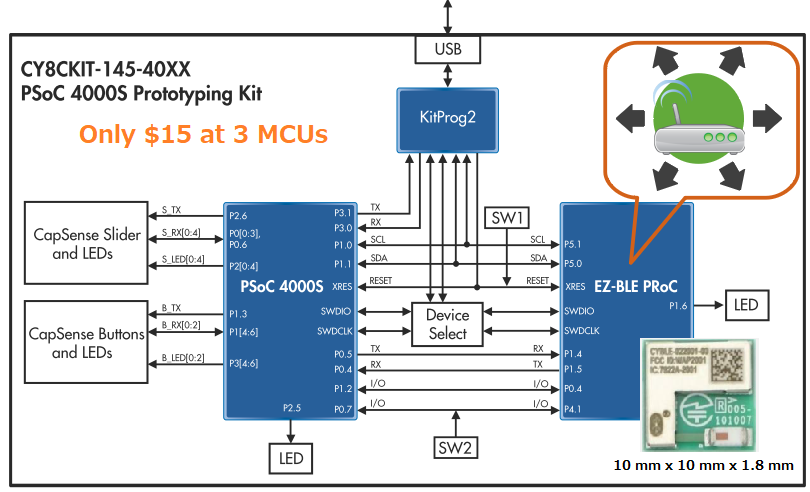

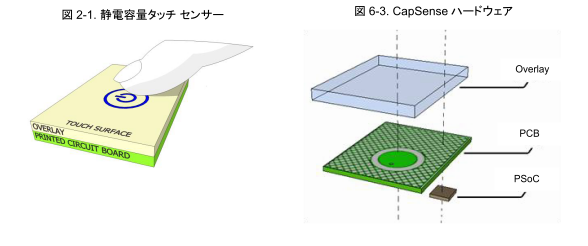

評価ボード:機能分割と低価格 本開発評価ボードのブロック図です。前章KitProg2とPSoC 4000S、さらにEZ-BLE PRoCの3MCU搭載でわずか$15です。

CY8CKIT-145-40XX_PSoC 4000S_Prototyping_Kit_Block Diagram EZ-BLE PRoC は、PSoC 4000SのEZ-I2Cコンポーネント経由で得たCapSenseボタンやスライド・バー位置を、スマホへのBluetooth無線送信する10 x 10 x 1.8mmサイズのモジュールです。スマホのアプリケーションは、Cypressサイトからダウンロードできます。

EZ-BLE PRoC用途 IoT MCUは、Bluetoothなどの無線通信やスマホ活用のエッジMCU制御も必要になります。

この開発に、無線機能付き高性能MCUを使って、RTOSやソフトウェア/ファームウェアを駆使し開発する選択肢もあります。が、評価ボードのようにモジュール分割し、複数の低価格MCUで組めば、わずか$15で実現できます。

しかも、機能分割した各MCUのソフトウェア開発も簡単です。EZ-BLE PRoCソースコードは、評価ボードサンプルプロジェクト内に有りますので参照してください。

評価ボードはバーゲンプライスです。しかし、その機能分割方法や評価ボードやモジュール活用のシステム開発も選択肢に入れるべきと感じる低価格と機能分割の上手さが解ります。低価格MCUでも使い方次第という好例が、本開発の評価ボードです。

PSoC 4000S/4100S内蔵、第4世代CapSenseの使い方(最終回:関連投稿)まとめ

ソフトウェア開発者向けPSoC 4000S/4100S第4世代CapSenseの使い方

項目 PSoC 4000S/4100S 内蔵第4 世代CapSense の使い方(要点)

タッチUI テンプレート構想

(その1)

単独タッチUIモジュール利用が可能

タッチUI ハードウェア

(その2)

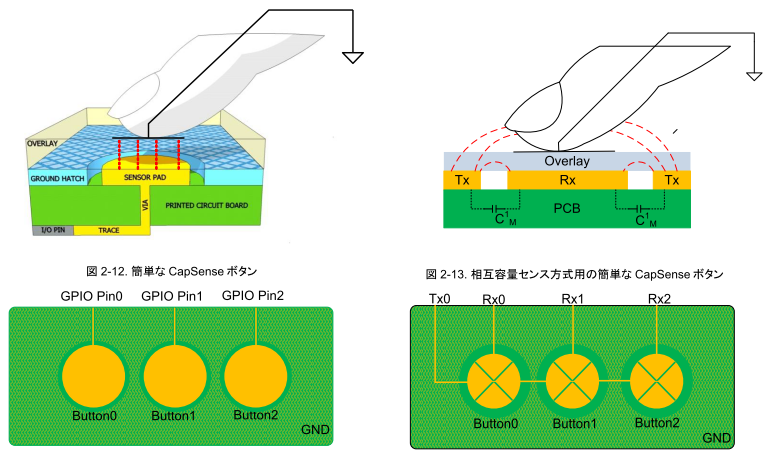

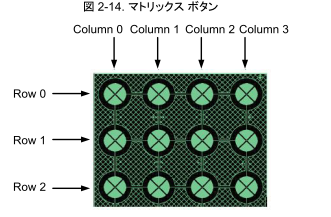

1. タッチUIは、指をパッドに近づけた時に生じる静電容量変化で検出。確実に静電容量変化を生むPCBハードウェア:パッド設計が重要。

2. ソフトウェア開発者向けPCB設計ガイドラインの要旨を示し、評価ボードパッド形状の理由と、自己容量式(self-capacitance)、相互容量式(mutual-capacitance)差を説明。

3. 評価ボードパッド部分をトラ技付録PSoC 4100S基板とも接続。 PSoC 4100Sでもテンプレートを動作させPSoC 4000S/4100S両方対応テンプレート化を図る。

CapSense 設定

(その3前半)

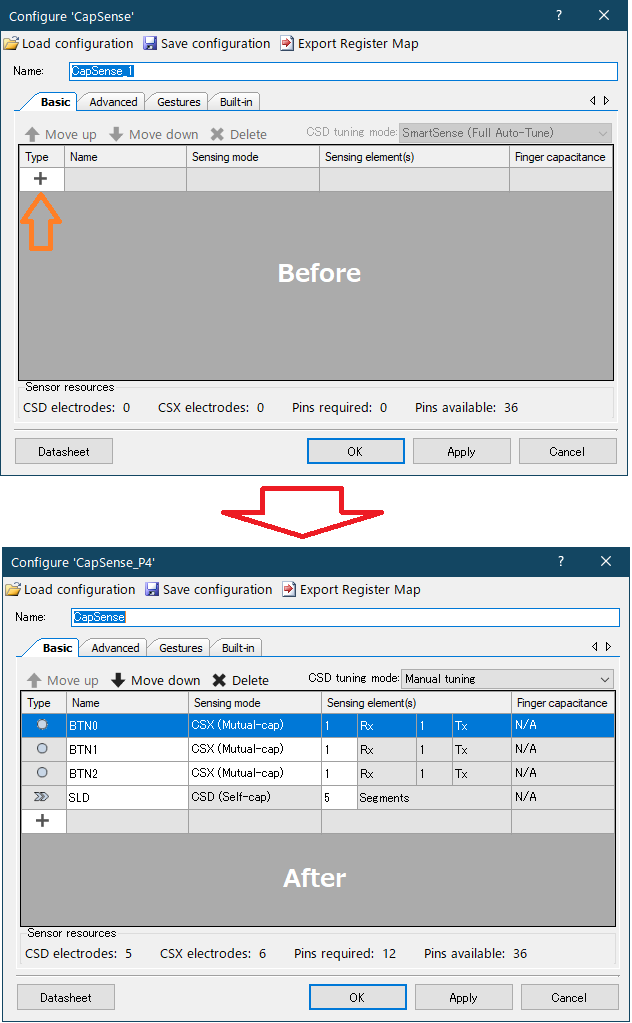

1. コンポーネントカタログからCapSenseを選びTopDesign.cyschへ配置。

2. コンポーネントデータシートを参照しCapSenseプロパティ設定。基本動作は、Basicタブ設定のみで十分。

3. CapSenseコンポーネント使用GPIOピン設定は、ピンエディタで実行。

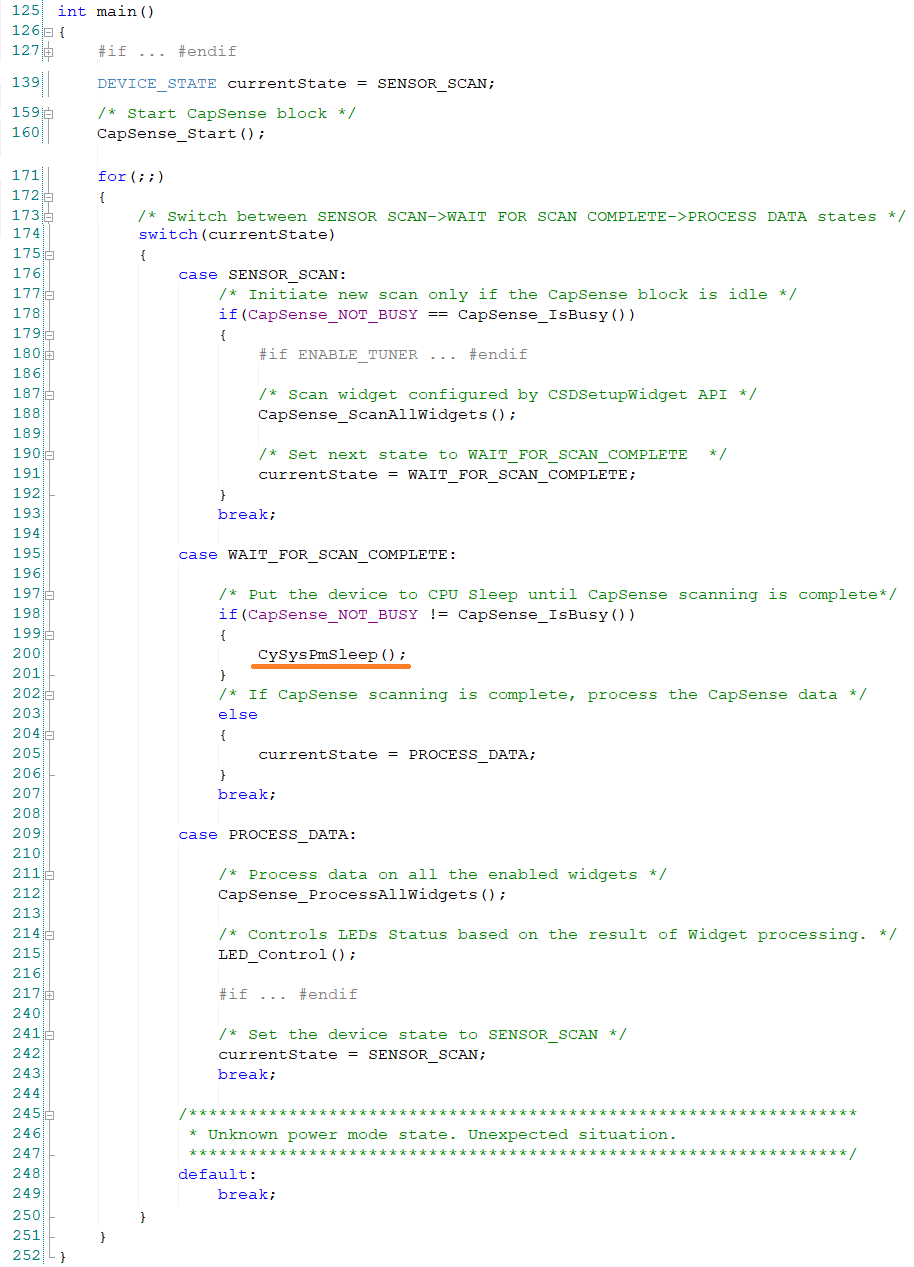

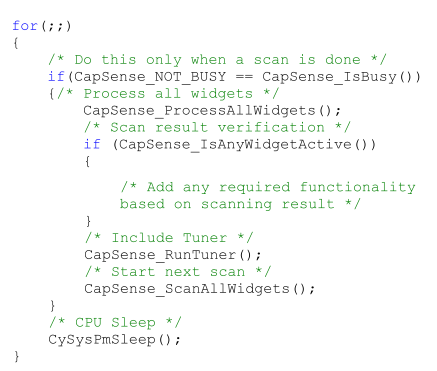

CapSense プログラミング

(その3後半)

1. 基本動作プログラミング教科書に評価ボードサンプルプロジェクトmian.cは最適。

2. 基本動作は、スキャン開始と終了の間、CPUスリープで低電力動作可能。

3. 高感度動作は、スキャン中別処理禁止のブロッキングスキャンを検討。

4. CapSenseプログラミングは、他コンポーネントとの並列処理より時分割処理の方がリスクは少ない。

5. 基本動作CapSense APIは6個。さらに多くのCapSense APIあり。

EZ_I2C (SCB )

(その4)

1. EZ-I2Cは、CapSense出力のリアルタイムモニタ用。

2. リアルタイムモニタは、ユーザ開発パッドのCapSenseプロパティ設定に役立つ。

3. EZ-I2Cは、SCBコンポーネント利用法:I2C通信の1種。

4. CapSenseとEZ-I2C間のデータ送受は、RAM利用。

わずか2個コンポーネント利用の第4世代CapSenseの使い方でも、初めてのPSoC MCU開発者向けに要点をまとめると上記になります。最新CapSense動作確認と、殆ど全てのPSoC MCU開発に必要になるSCBコンポーネントの習得が、評価ボードで手軽にできるので教材としては最適だと思います。

PSoC MCUは、コンポーネント単位の開発経験積重ね ができます。

一度PSoC開発を経験しておけば、新しい内容はCapSenseプログラミングだけです。今後は開発アプリケーションに応じて使用するコンポーネントを段階的に増やし、PSoC MCU開発の面白さ、奥深さを実感、習得してください。

但し、新規にプロジェクトを開発する時でも、1からコンポーネントを積重ねるのは非効率です。

PSoC Creatorには、新規プロジェクト開始時にPre-populated schematicというプリセット型プロジェクトもあります。しかし、より実務的でプロトタイプ開発に適し、時分割処理を組込んだプロジェクト、これが弊社テンプレート です。

弊社テンプレートは、プロジェクト開始時に最低限必要なコンポーネントが組込み済みで、プロトタイプ開発スピードを上げる効果があります。また、時分割処理ですので、コンポーネント単位の処理追加・削除も容易です。

関連投稿:テンプレート利用Tips

新開発のPSoC 4000S/4100SタッチUIテンプレート発売は、2019/3Q予定です。

このテンプレートをご購入頂ければ、本稿のまとめ文章だけでなく、豊富な日本語コメント付きソースコードと、開発 Know How なども記載した資料 が付属します。より具体的に、しかも初心者・中級者にありがちな開発トラブルを回避した第4世代PSoC 4000S/4100S CapSenseの使い方、PSoC MCU開発が短期で効率的に習得できます。