ルネサスRAファミリ評価ボードの動作テストプログラムと、周辺回路サンプルコードから判るRAファミリアプリケーション開発Tipsを示し、このTipsで開発したアプリケーション:App0を公開します。

評価ボードは、RA6E1を用いましたが、他のRAファミリ評価ボードでも同じです。

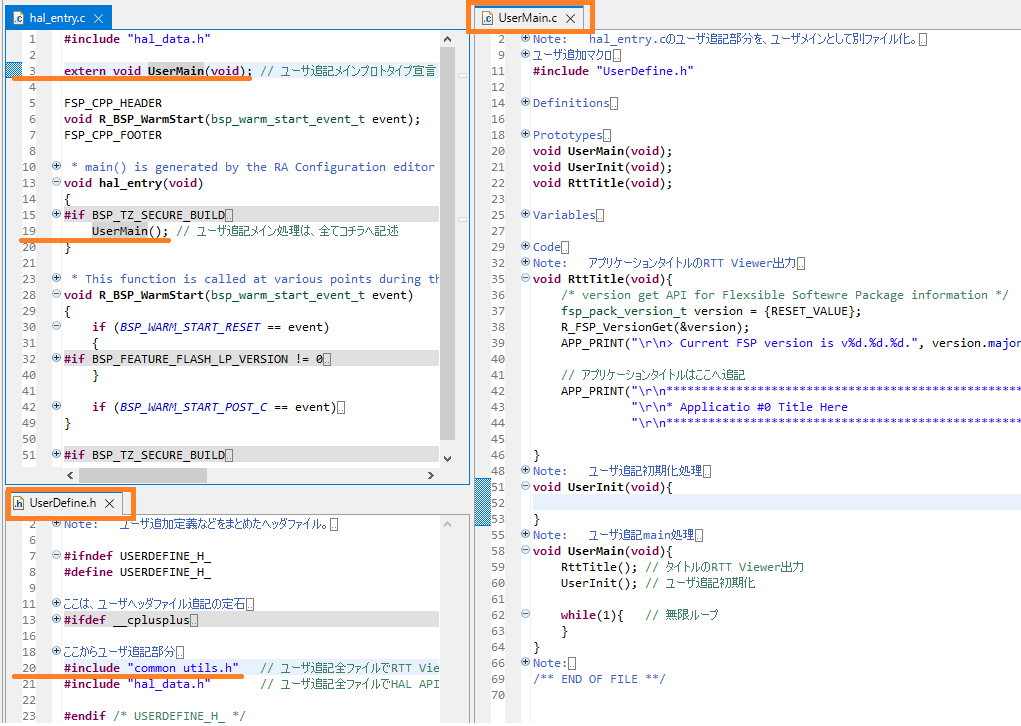

hal_entry.cとuser_main.c分離

RAファミリは、評価ボード毎にサンプルコードが提供されます。例えば、RA6E1の場合は、FPB-RA6E1 Example Project Bundleがそれで、この中にADCやタイマなどの周辺回路サンプルコードがあります。また、評価ボードテストプログラム:TP(quickstart_fpb_ra6e1_ep)も含まれており、他の周辺回路サンプルコード:EP(Exampleプログラム)とは少し違うファイル構造になっています。

違う原因は、EPが、コード判り易さのため、メイン処理をhal_entry.cに集中して記述するのに対し、TPは、様々な評価ボードへも対応するため、いわば汎用アプリケーション構造となっているからです。

簡単に言うと、FSPが生成するメイン処理:hal_entry.cと、ユーザ追記のメイン処理:user_main.cをファイル分離し、ユーザ開発部分の可搬性を上げた構造を持つのがTPです。

開発したMCUアプリケーションに可搬性があると効率的で生産性もあがります。TP同様、RAアプリケーションも、hal_entry.cとuser_main.cを分離した構造で開発する方法をお勧めします。

※FSP(Flexible Software Package)やサンプルコードの詳細は、コチラの関連投稿を参照ください。

SEGGER RTT Viewer利用

TPとEPには、もう1つ違いがあります。それは、EPには、PC入出力マクロが実装済みの点です。

例えば、gpt_fpb_ra6e1_ep(最初のgptが汎用PWMタイマ、fpb_ra6e1が評価ボード、epがExample Programを示す)ならば、タイマ利用例をPCへ出力し、その設定値をPCから入力できます。

対PC通信にはUSB経由Virtual COMポートを利用する評価ボードが多いのに対し、ルネサスRAファミリは、評価ボード実装デバッガのSEGGER RTT Viewerをこの役目に使います。USARTなどのMCU資産を消費しないメリットがあります。

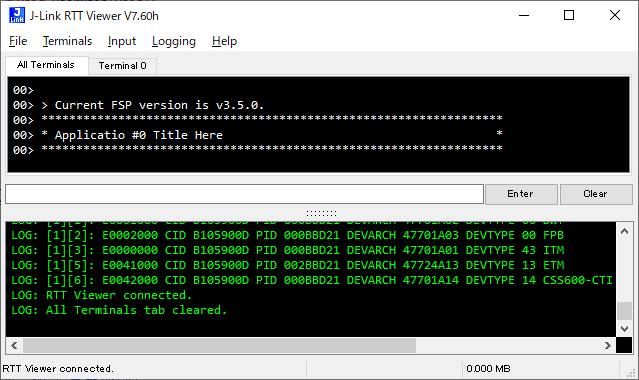

PCでRTT Viewerを使うには、コチラからJ-Link Software and Documentation Packをダウンロードし、PCへインストール後、J-Link RTT Viewer起動で評価ボードとPC通信ができます(最初の図)。

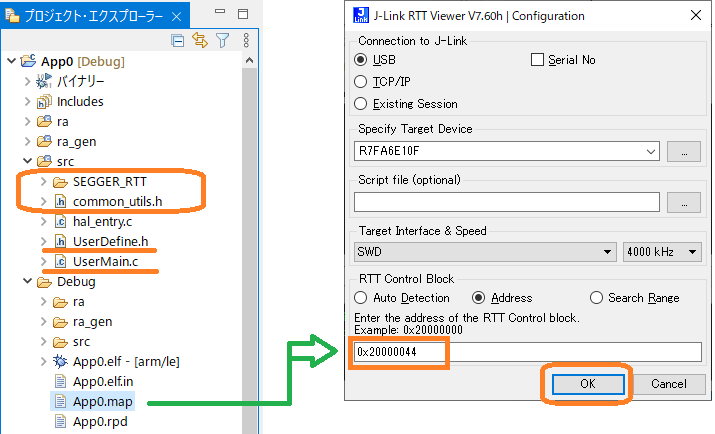

但し、RA6/4などCortex-M33コアファミリ開発の場合は、ビルド後生成されるmapファイルからRTT Control Block Addressを探し、Viewer起動ダイアログへ入力する必要があります。

プログラム変更やFSP版数が変わると、このBlock Addressも変わるので、生成mapファイルAddress値の再入力が必要です。

RAアプリケーション開発時にも、このPC通信マクロが使えるとprintf/scanfの代用になり便利です。FSP生成プロジェクトでPC通信マクロを利用するには、生成プロジェクトのsrcフォルダへ、SEGGER_RTTとcommon_utili.hの両方を手動で追加します。

追加元のSEGGER_RTTとcommon_utili.hは、どのEPのものでも構いません。

App0特徴

以上から、RAアプリケーション開発時は、FSPが生成するオリジナルファイルに

①HAL生成メインhal_entry.cとユーザ追記メインuser_main.cを分離したファイル構造

②srcへSEGGER_RTTとcommon_utility.hの手動追加

を行うと、ユーザ開発ソースコードのRAファミリ間での可搬性が高く、PC通信も容易なアプリケーションの骨格(Skelton)が完成します。

この方法で開発したアプリケーション:App0を示します。タイトルをPCへ出力するだけのアプリケーション骨格です。この骨格に、開発ソースコードを肉付けしていけば、肉付けソースコードのRAファミリ間可搬性が高く、デバッグ効率も高いアプリケーション開発ができます。

開発したApp0プロジェクト圧縮ファイルは、コチラよりダウンロード可能です。ご自由にご利用ください。

e2 studioへのインポート方法は、インポート>既存プロジェクトをワークスペースへ>アーカイブ・ファイルの選択で、App0.zip指定です。

App0開発手順

以下にApp0プロジェクトの作成手順を示します。

1)FSPで新規Bare Metal – Minimalプロジェクト生成

2)App0 FSPパースペクティブでGenerate Project Contentクリック

3)他の周辺回路サンプルコードのsrc>SEGGER_RTTとcommon_utility.hをコピーし、App0プロジェクト>srcフォルダへペースト

4)src>hal_entry.cのL3へextern void UserMain(void)追記、L19へUserMain()追記

5)src上で新規>ソース・ファイルをクリックし、UserMain.c追加

6)src上で新規>ヘッダー・ファイルをクリックし、UserDefine.h追加

7)UserMain.cとUserDefine.hへ、前章ソースコード追記

8)ビルドし、Debug>App0.mapファイルから_SEGGER_RTTを検索、そのアドレスを、RTT Viewer起動ダイアログのRTT Control Blockへ入力後OKクリック

9)評価ボードへApp0をダウンロード、実行

10)PCのRTT Viewerで図1のタイトル出力確認

4、5、6の追加ファイル名は、UserMain.c、UserDefine.hなど先頭大文字のPascal形式を用いています。これは、プロジェクト・エクスプローラーでオリジナルのFSP生成ファイルとユーザ追加ファイルの識別が容易になるからです。

また、筆者は、Cソース・ファイル毎にヘッダー・ファイルを追加するより、ソース・ファイル内にプロトタイプ宣言を追記し、個別ヘッダー・ファイルを追加しない方が好みです。4のhal_entry.cへUserMainプロトタイプ宣言を追記したのも、このためです。

UserMain()は、初期設定と無限ループに分け、初期設定にRttInit()とUserInit()を追加しています。RttInit()でタイトルをPCへ出力し、UserIint()は、内容が何もありません。骨格ですので、利用する周辺回路に応じて、ここへ初期設定コードを追記することを想定しています。

まとめ

RAファミリ評価ボードテストプログラムと周辺回路サンプルコードから、hal_entry.cとuser_main.cの分離ファイル構造と、RTT Viewer利用の対PC通信マクロ実装済みのアプリケーションスケルトン(骨格):App0を示しました。

この骨格へ、開発ソースコードを追加していけば、ユーザ追加部分のRAファミリ間可搬性が高く、デバッグ効率も高い、RAファミリアプリケーションが開発できます。

もちろん、3月末を目標に開発中のRAファミリテンプレートも、このApp0へ評価ボード実装LED点滅やチャタリング対策済みSW機能などを追加します。RAファミリテンプレート構想はコチラの4章、RAテンプレートの仕組みはコチラの関連投稿を、参照ください。