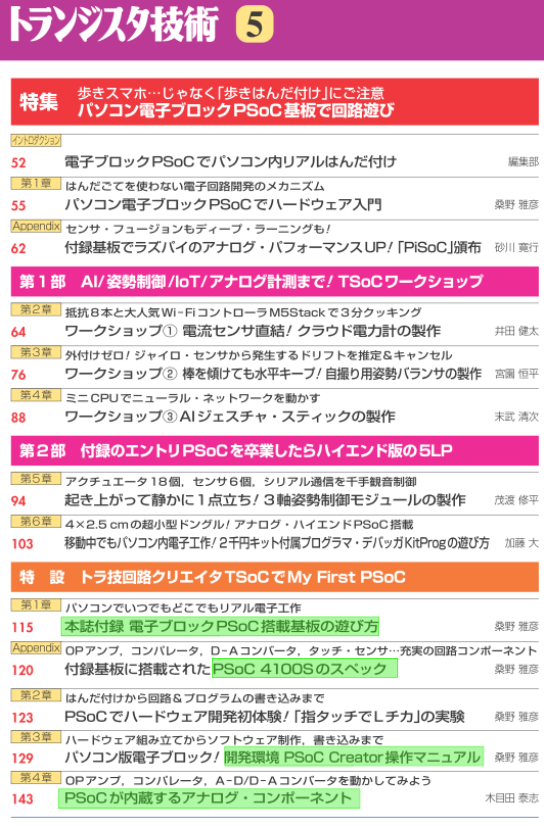

MCU:マイコンは、種類が多くどれを自分の開発や製品に使うのが最適か?分りにくいと言われます。この問いに対する回答を示します。具体例として今年5月トランジスタ技術で紹介されたCypress PSoC 4シリーズのMCUを選択します。他ベンダでも同様です。

MCU選択とスマホ選択の差

毎年新機種が発表されるスマートフォン。特にAndroidスマホは、電話の基本機能は同じでも、カメラなどの付加機能やサービス、価格帯が広く、選択に迷います。それでも、何年かスマホを使っていると、どの機能が自分に必須かが分かってくるのと懐具合との兼ね合い、また、古い機種は数年でカタログから消えるので、スマホ選択幅は収束します。

ところが、MCUの場合は、発表後10年以上販売継続されます。スマホとの一番の差です。

古い選択肢も残ったまま新製品が追加され、選択幅が時間とともに広がるのがMCU選択を困難にする要因の1つです。

そこで、広い選択幅からMCUを選ぶ方法を、4段階で示します。

第1段階:適用製品による大枠選択

MCUベンダは、適用製品に合わせてMCUを大分類します。車載とインダストリアル分野では使用温度や内蔵周辺回路などの要件が異なるからです。そこで、第1段階は、この適用製品でMCUを選択します。

例えば、NXPやSTマイクロエレクトロニクストップサイトの“アプリケーションタブ”がこの大枠を示します。

ルネサスエレクトロニクスやCypressの場合は、“ソリューションタブ”です。

ここまでは、多くの方がご存じと思います。分かりにくくなるのは、ココカラです。

第2段階:MCU名称による中枠選択

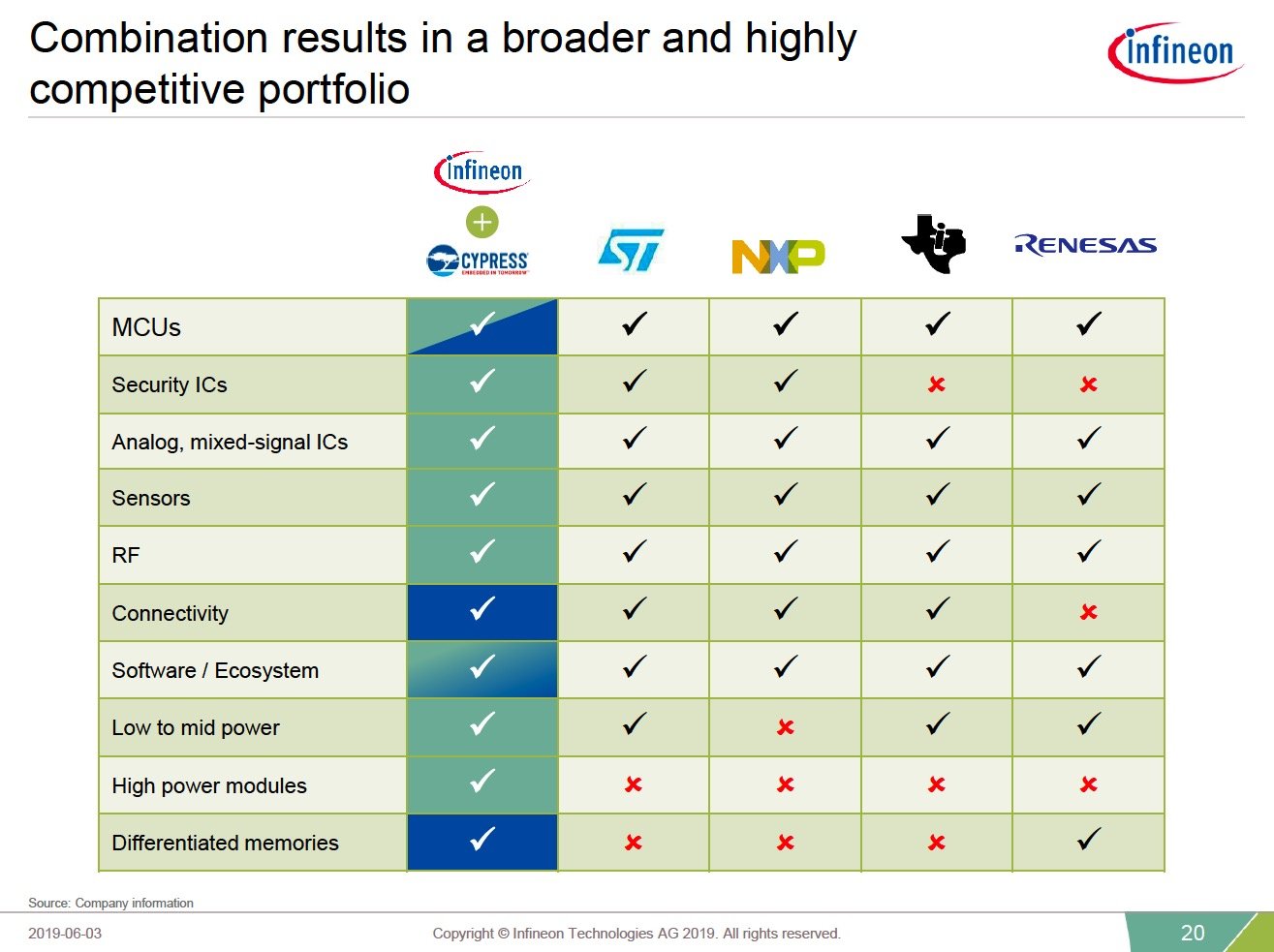

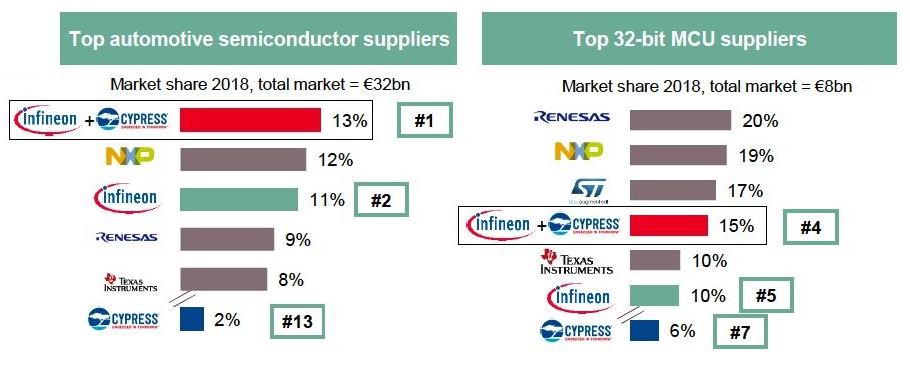

同じインダストリアル分野のMCUでも、シリーズやファミリなど細かく名称が分かれています。名称が異なるには訳があるので、その理由を理解するのが、第2段階です。この段階では、ベンダ間の買収や合併などの歴史も知っている方が良いです。ポイントは、選択の決め手となる最新カタログの取得です。

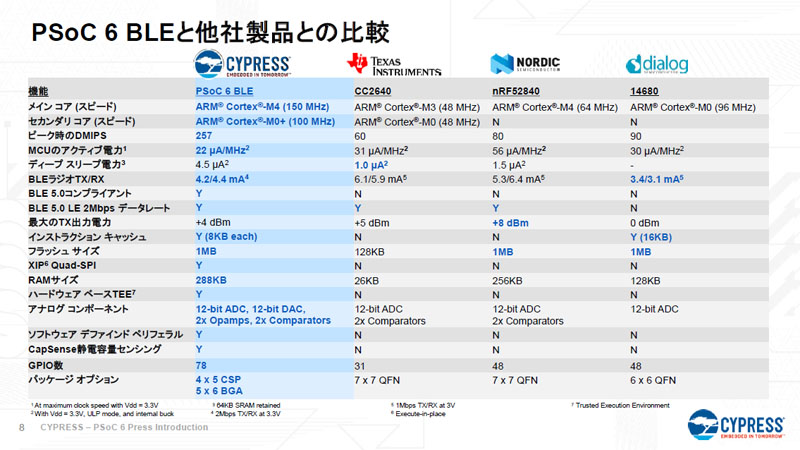

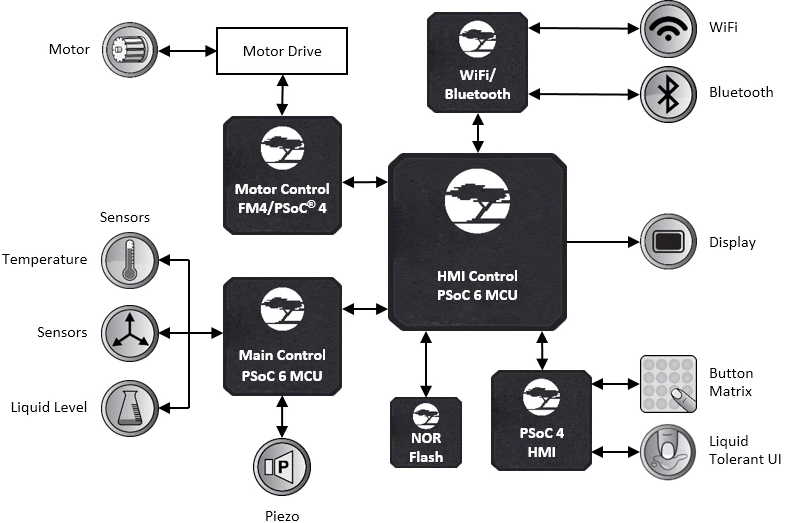

Cypressのスマートアプリケーション分野のMCUで説明します。

PSoC 6/4/FM4などの複数MCUから構成されるスマート洗濯機です。PSoC X(X=4,6)は、元々のCypress MCUの名称で、FM4は、2014年に合併した米Spansion(実はSpansionに買収された富士通セミコンダクター)のMCU名称です。

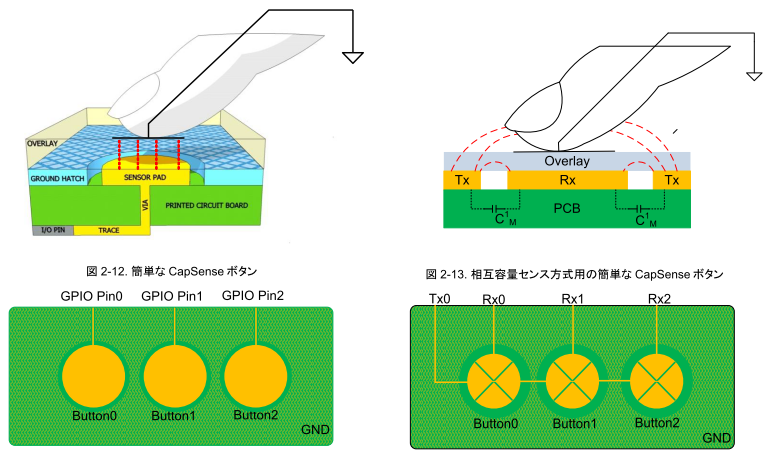

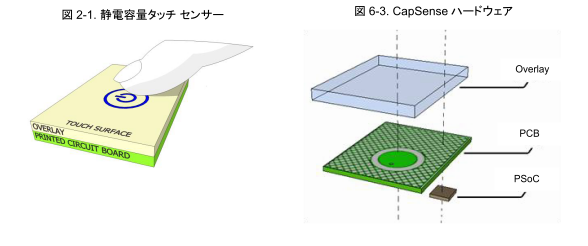

Cypressは、Spansion合併でARM Cortex-M0+ライセンスを取得し、Cortex-M0利用のPSoC 4に適用、その結果生まれた新製品がPSoC 4Sです。PSoC 4Sは、特許取得済み静電容量式第4世代タッチセンサCapSense内蔵のPSoC 4000ファミリへと発展しました。

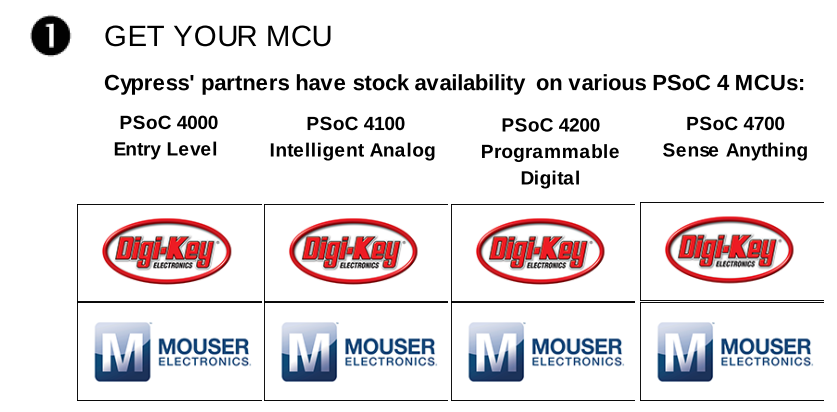

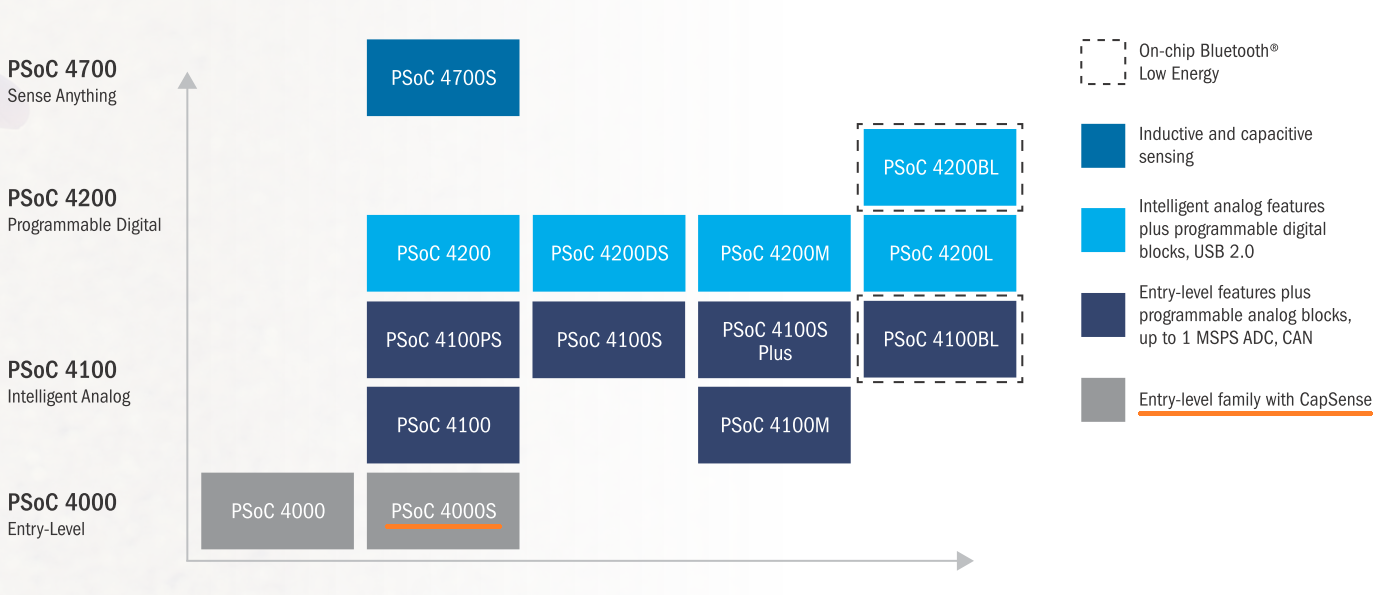

PSoC 4サイトトップページへ行き製品タブを見ると、さらに細かくPSoC 4000/4100/4200/4700とファミリが分類されており付加機能も異なります。この中枠の段階で製品セレクターガイドなどへ行くとMCU選択に迷ってしまします。他のベンダでも同様です。

この中枠MCU選択の重要資料:Brochureをダウンロードします。Brochureとは、製品パンフレット、カタログのことで、ほぼ毎年更新されます。

どのベンダでも、この中枠MCUを対象とした製品カタログがあります。この最新カタログを見つけるのがMCU選択での最重要事項です。

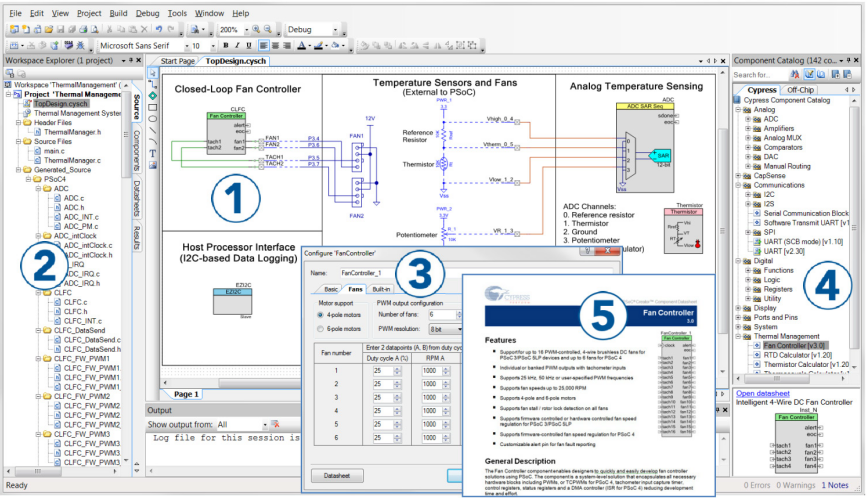

第3段階:最新カタログと評価ボードによる開発MCU選択

製品カタログには、ベンダがアピールしたい最新MCU情報が詳しく掲載されます。継続販売中の古いMCUや歴史は(紙面の都合上)無視されます。但し、これで新旧MCUを選択のふるいにかけることができます。

世間の話題にはなりにくいMCUの発展速度も、スマホやPC並みに早いのです。最新MCUは、低電力動作や処理効率に優れ、市場ニーズに即した開発が期待できます。

製品カタログには、中枠に相当するMCUファミリ一名称や概略を示す一覧図が掲載されます。

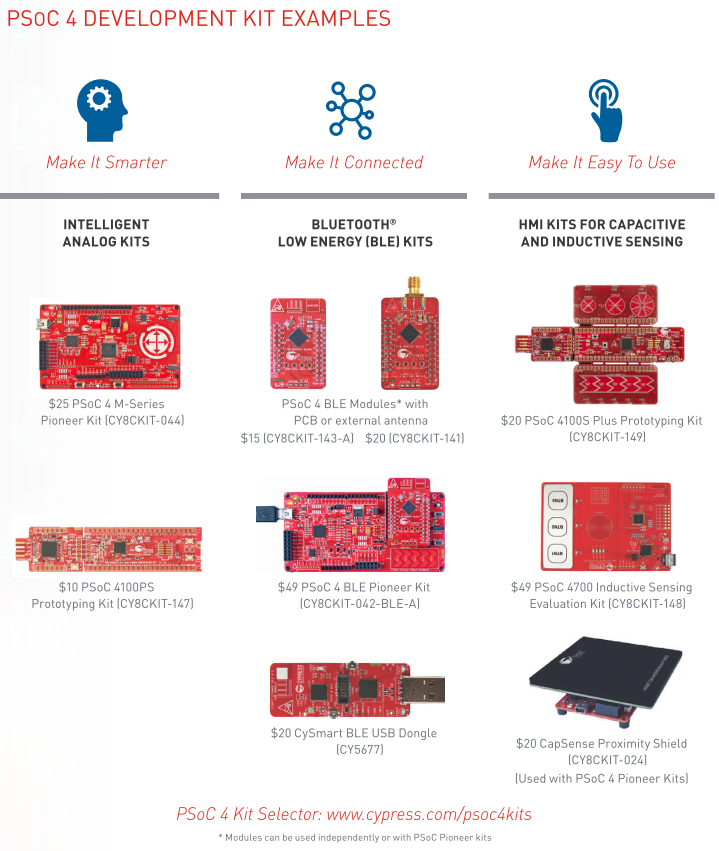

PSoC 4の場合は、下図です。ファミリ名の差(=意味)をこの図から理解すれば、開発MCU選択は、殆ど(?!)最終段階です。

殆どとは、例えば、エントリーレベル灰色の四角:PSoC 4000SファミリにもFlashやROM、内蔵周辺回路数により多くのMCUがあります。つまり、開発に適すMCUを各四角の中から選択する必要がある訳です。

これには、ファミリ毎にベンダが用意する評価ボード搭載MCUが適します。カタログにも評価ボードが記載されています。

評価ボード搭載MCUは、ファミリ内で最も標準的かつ応用範囲が広く、しかもサンプルコードが付いていますので、MCUを直に動作させることができます。低価格で入手性が良いのも特徴です。開発着手のMCUとしては最適です。

第4段階:プロトタイプ開発による製品MCU選択

評価ボードのMCUを基準にプロトタイプ開発を行い、製品化時のMCU選択をします。

プロトタイプMCUでFlash/RAM不足が懸念されならより大容量MCU、性能不足や周辺回路数不足が懸念されるならより高性能MCUを製品MCUとして選択するなどです。プロトタイプ開発により、製品MCU評価が高精度でできます。

以上の4段階で開発や製品に適すMCU選択ができます。プロトタイプ開発結果をどう活かすかで最適な製品MCU選択ができます。

Cypress PSoC 4 MCU選択具体例

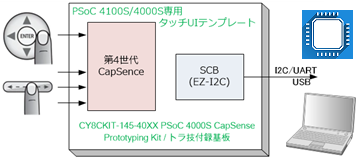

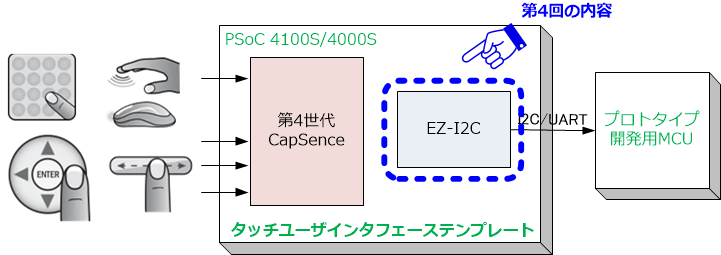

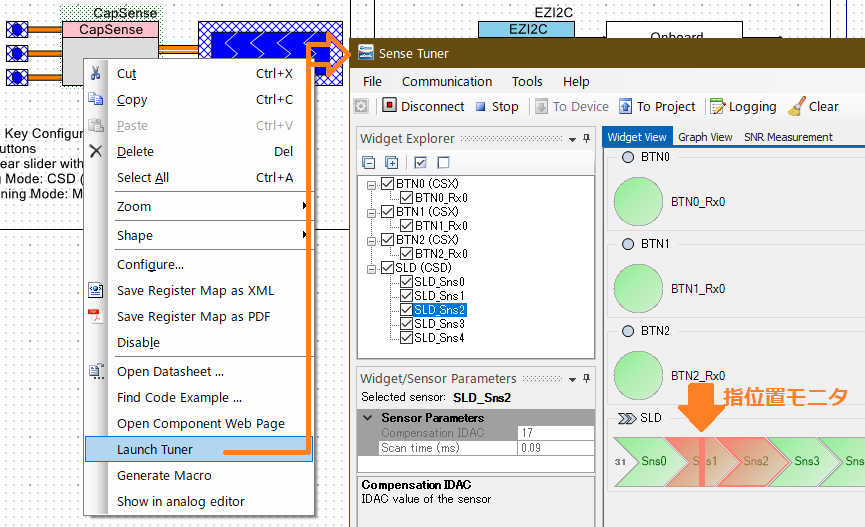

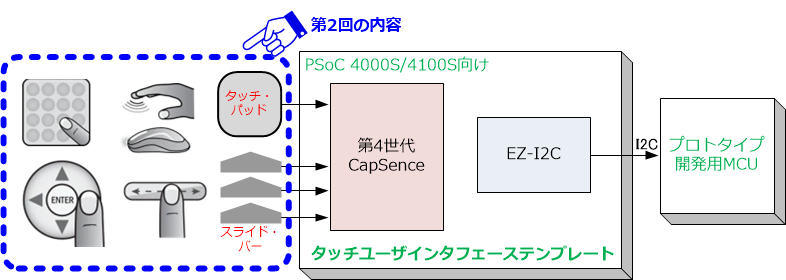

弊社開発中のCapSenseテンプレートに用いるCypress PSoC 4 MCUを、上記の方法で選択した結果を示します。

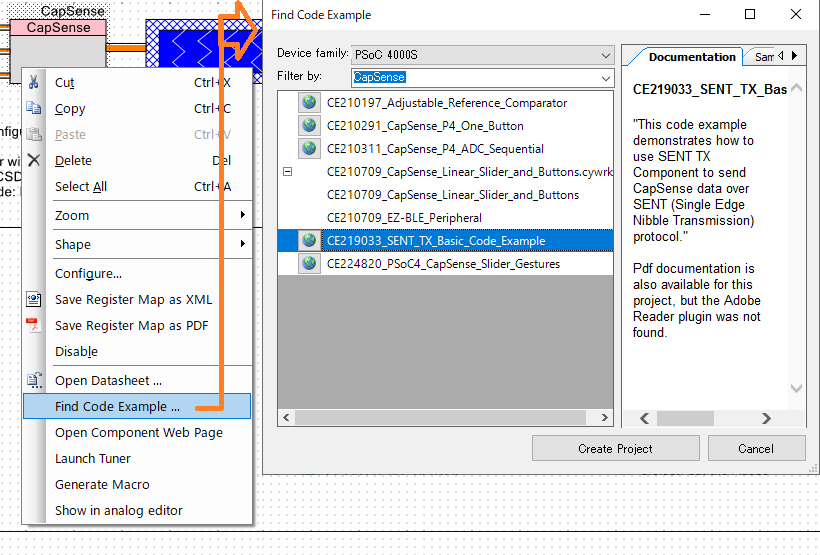

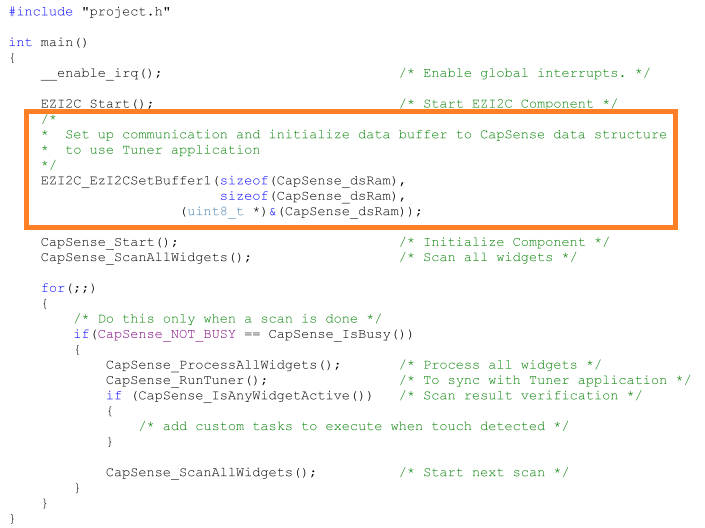

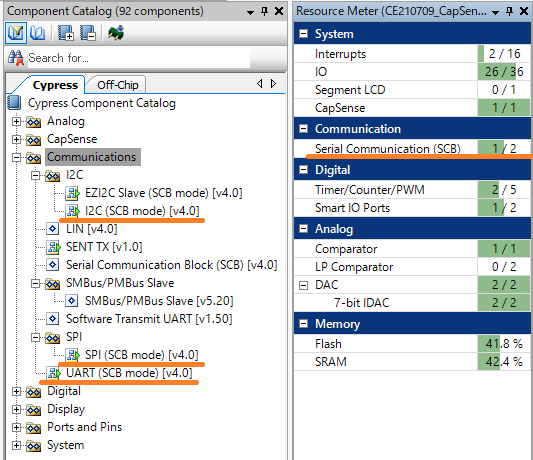

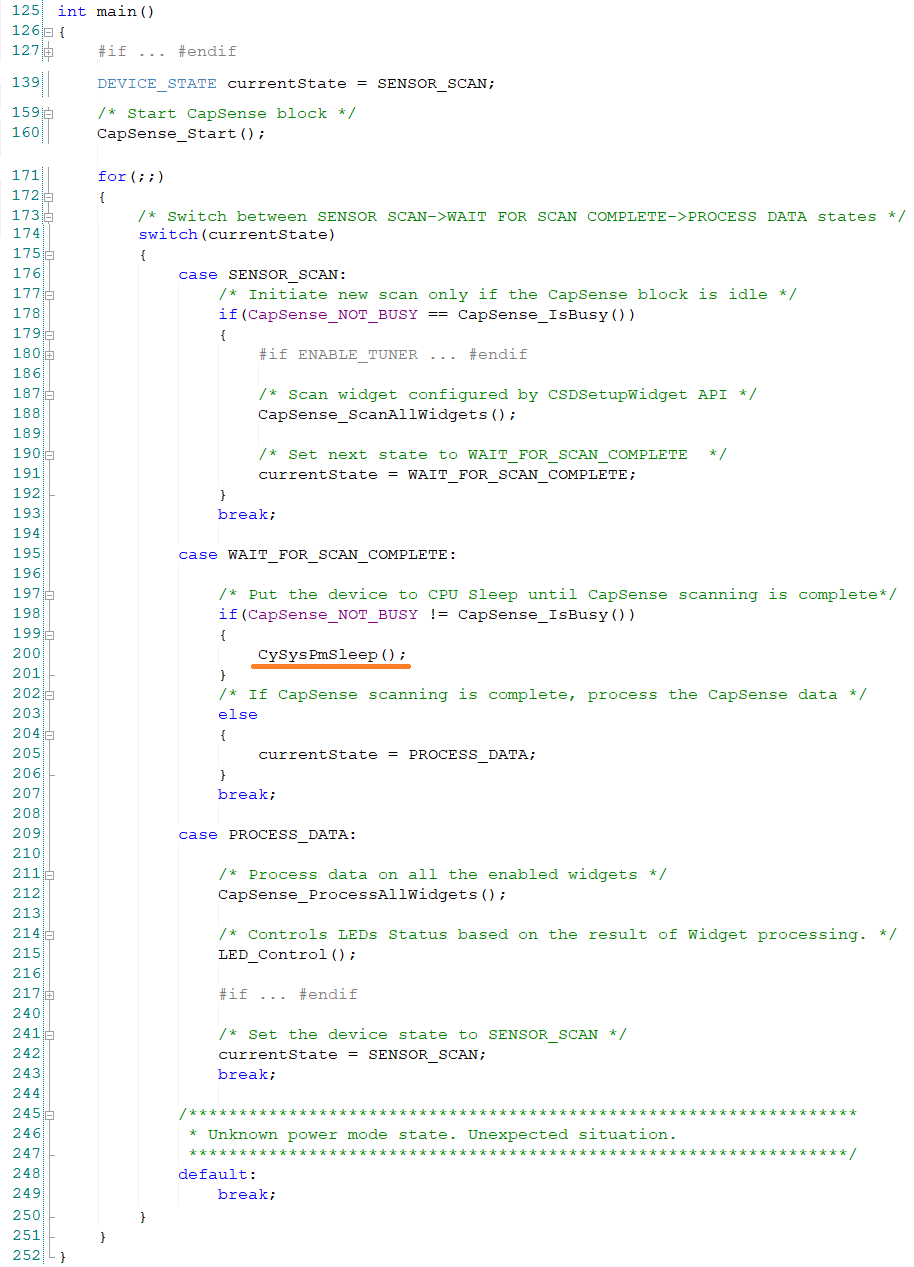

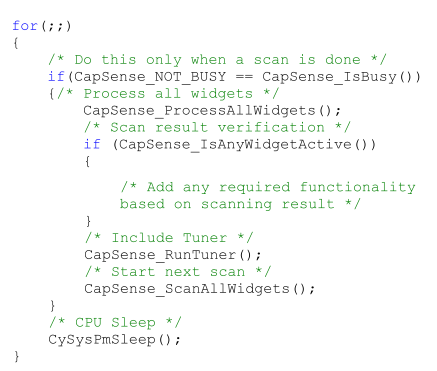

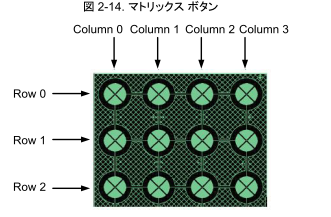

CapSense は、PSoC 4000ファミリの他社差別化機能の1つです。そこで、このCapSenseを活かすプロトタイプ開発テンプレートを目指します。

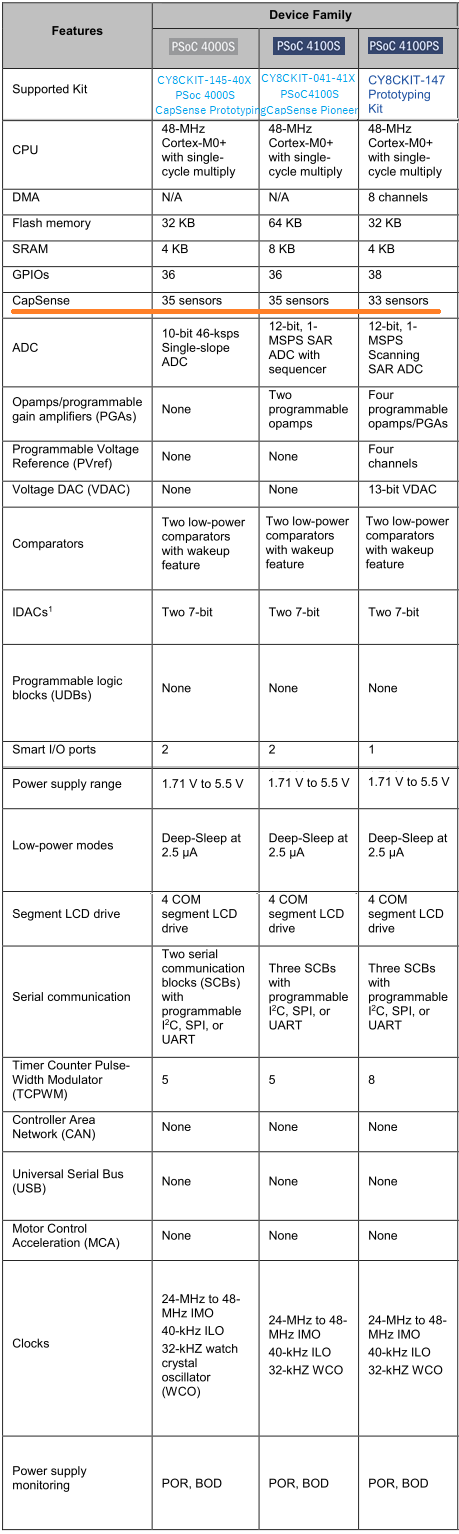

CapSenseテンプレートに用いる3ファミリMCU:PSoC 4000S、PSoC 4100S、PSoC 4100PSの特徴を一覧で示します(縦長の図がウェブでは上手く表示できます)。

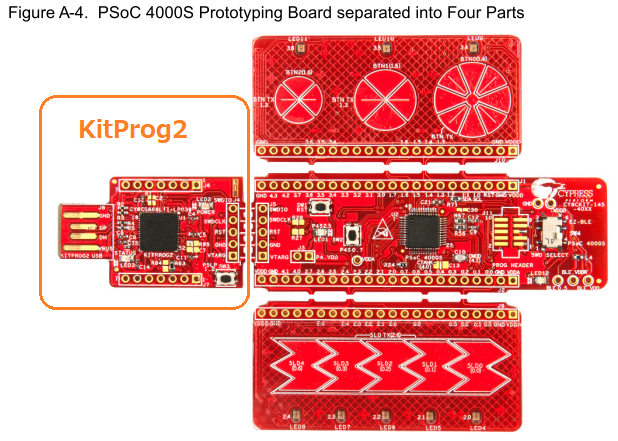

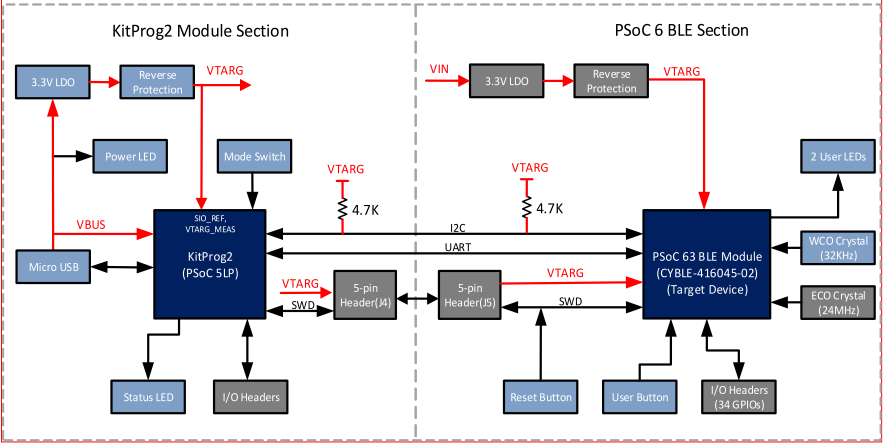

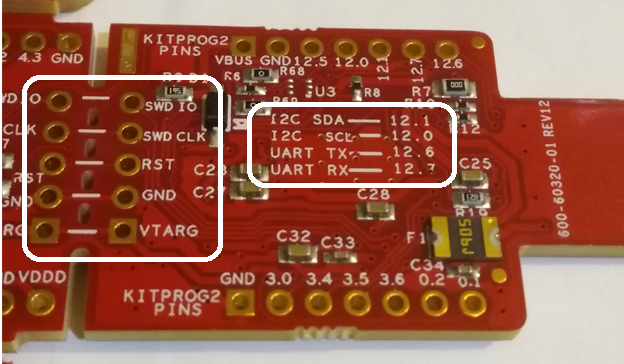

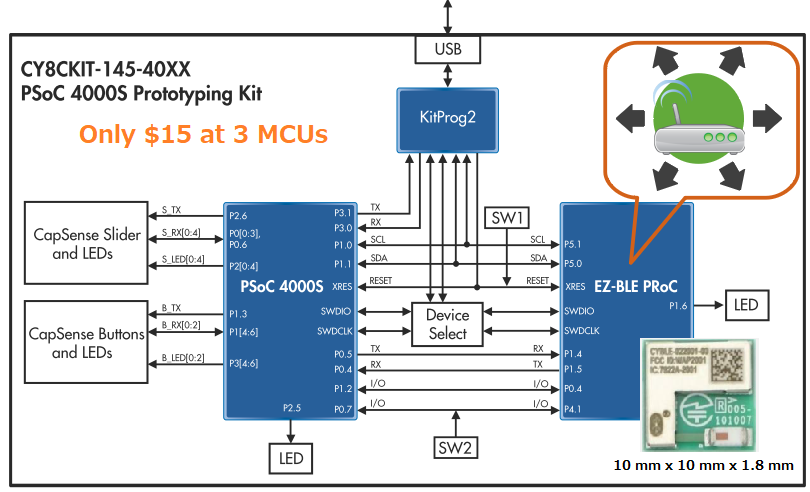

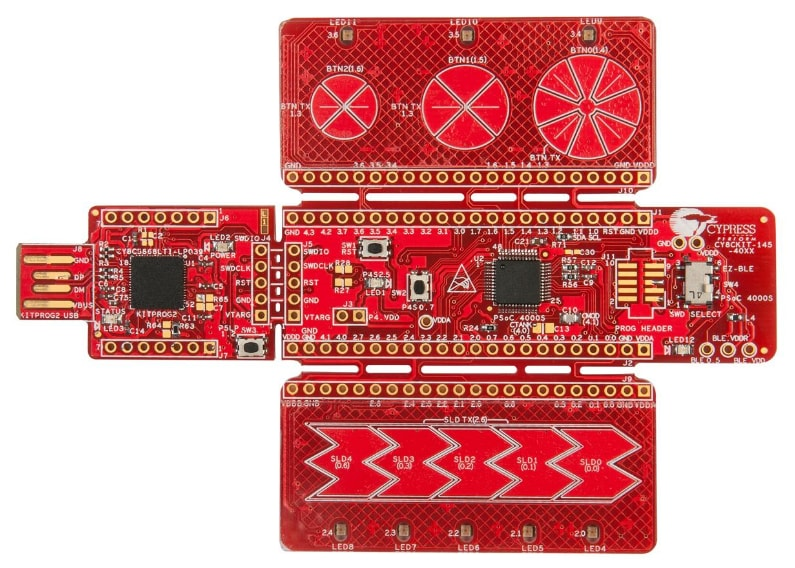

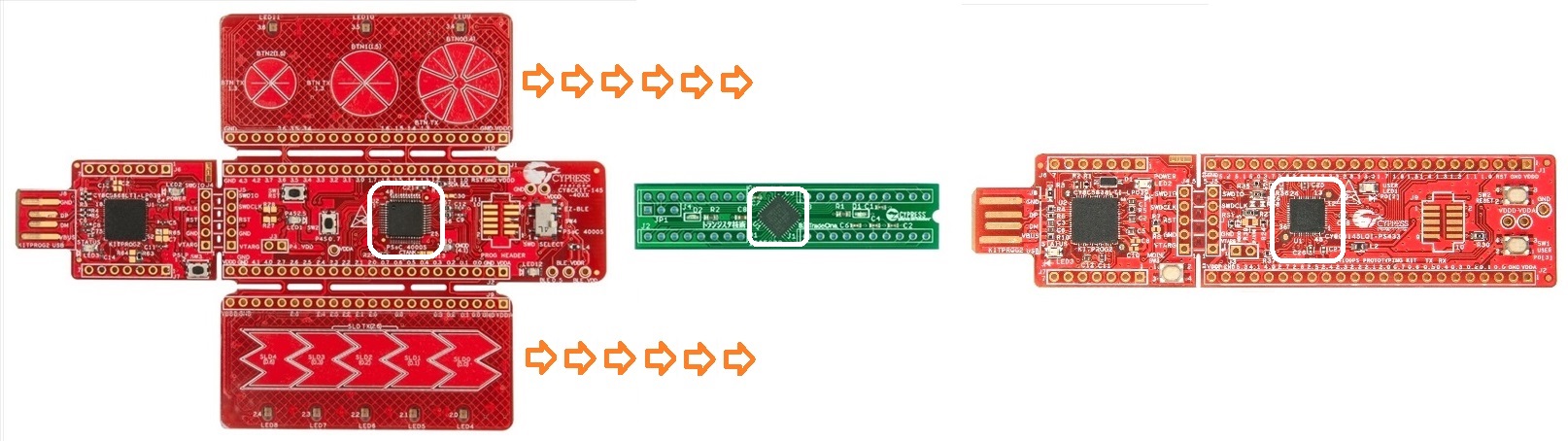

PSoC 4000S評価ボード:CY8CKIT-145-40XX PSoC 4000S CapSense Prototyping Kit搭載MCUは、CY8C4045AZI-S413(48ピン)です(下図左)。

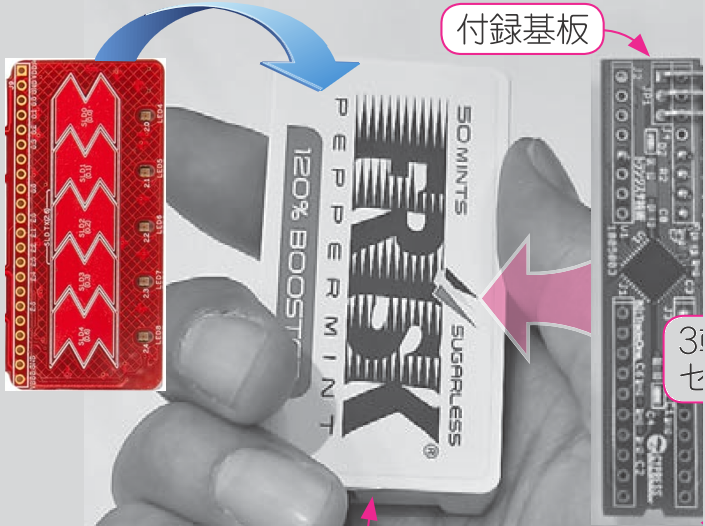

PSoC 4100S評価ボード:CY8CKIT-041-41XX PSoC 4100S CapSense Pioneer Kit搭載MCUは、CY8C4146AZI-S433(48ピン)です。トラ技5月号付録PSoC 4100S基板実装のCY8C4146LQI-S433(40ピン)も同じファミリですが、ピン数のみが違います(下図中央)。

PSoC 4100PS評価ボード:CY8CKIT-147 Prototyping Kit搭載MCUは、CY8C4145LQI-PS433(48ピン)です(下図右)。

Cypressの3ファミリ評価ボードは、どれも48ピンで揃っているので、比較しやすいでのすが、弊社は、予算の都合上、PSoC 4100Sファミリは、トラ技付録PSoC 4100S基板実装MCU(40ピン)を用います。

CapSenseで最重要なタッチUIハードウェアは、PSoC 4000S評価ボードのCapSense基板を、PSoC4100S/4100PS各基板と接続してテンプレート動作確認をします。PSoC 4000S → PSoC 4100SでFlash/RAM容量増加、PSoC 4000S → PSoC 4100PSでアナログフロントエンド強化などへ発展します。

※CapSenseテンプレート完成は、計画当初は2019Q3でした。しかし、PSoC 4100PS評価ボードは、トラ技懸賞品をあてにしており、運よく当選し11月Mに当選品が入手できました。2019Eを目途にテンプレート完成の予定です。